AN ISO SOCIO REPORTE CONTRARA

# Atmel Corporation Enhanced RISC Microcontrollers Data Book

May 1996

**Preliminary**

is the registered trademark of Atmel Corporation, 2325 Orchard Parkway, San Jose, CA 95131

## Important Notice

Atmel guarantees that its circuits will be free from defects of material and work-manship under normal use and service, and that these circuits will perform to current specifications in accordance with, and subject to, the Company's standard warranty which is detailed in Atmel's Purchasing Order Acknowledgment.

Atmel reserves the right to change devices or specifications detailed in this data book at any time without notice, and assumes no responsibility for any errors within this document. Atmel does not make any commitment to update this information. Atmel assumes no responsibility for the use of any circuits described in this data book, nor does the Company assume responsibility for the functioning of undescribed features or parameters.

In the absence of a written agreement to the contrary, Atmel assumes no liability with respect to the use of semiconductor devices described in this data book for applications assistance, customers' product design or infringement of patents or copyrights of third parties.

Atmel's products are not authorized for use as critical components in life support devices or systems and the use as such implies that user bears all risk of such use.

If Atmel is an approved vendor on a Standard Microcircuit Drawing (SMD), the Atmel similar part number specification is compliant with the SMD.

© Atmel Corporation 1996

Printed on recycled paper.

Atmel Corporation designs, manufactures, and markets high quality and high performance CMOS memory, logic and analog integrated circuits. Founded in 1984, the Company serves the manufacturers of computation, communications and instrumentation equipment in commercial, industrial and military environments.

Atmel's broad line of products provide customers with a variety of solutions to their memory and logic applications. Atmel offers high-density, high-speed memory and logic standard products as well as custom gate arrays.

Atmel guarantees quality and reliability by fabricating all products— no matter what their intended application— to meet or exceed the specifications of Military Standard 883.

Whether you are new to programmable logic or an experienced user, Atmel is committed to your success. If you have any questions or would like to place an order, please contact your local Atmel sales office as listed in the back of this data book, or contact Atmel's corporate headquarters:

Atmel Corporation 2325 Orchard Parkway San Jose, CA 95131 TEL: (408) 441-0311 FAX: (408) 436-4300 Fax-on-Demand

North America:

1-(800) 29-ATMEL

1-(800) 292-8635

International:

1-(408) 441-0732

e-mail

literature@atmel.com

Web Site

http://www.atmel.com

BBS

1-(408) 436-4309

We thank you for considering Atmel semiconductors. AVR is a trademark of Atmel Corporation.

# Table of Contents

| Section 1 | Overview                                               |             |  |  |  |  |

|-----------|--------------------------------------------------------|-------------|--|--|--|--|

|           | <b>AVR</b> <sup>™</sup> Enhanced RISC Microcontrollers | 1-1         |  |  |  |  |

|           |                                                        |             |  |  |  |  |

|           |                                                        |             |  |  |  |  |

|           |                                                        |             |  |  |  |  |

| Section 2 | AT90S1300                                              |             |  |  |  |  |

|           | Description                                            | 2-3         |  |  |  |  |

|           | Pin Configuration                                      | 2-3         |  |  |  |  |

|           | Block Diagram                                          |             |  |  |  |  |

|           | Pin Descriptions                                       |             |  |  |  |  |

|           | AT90S1300 AVR Enhanced RISC Microcontroller CPU        | 2-7         |  |  |  |  |

|           | Timer / Counters                                       |             |  |  |  |  |

|           | The Watchdog Timer                                     |             |  |  |  |  |

|           | EEPROM Read/Write Access                               | 2-21        |  |  |  |  |

|           | The Analog Comparator                                  | 2-22        |  |  |  |  |

|           | I/O-Ports                                              |             |  |  |  |  |

|           | Memory Programming                                     |             |  |  |  |  |

|           | Absolute Maximum Ratings                               | 2-39        |  |  |  |  |

|           | DC Characteristics                                     |             |  |  |  |  |

|           | External Clock Drive Waveforms                         |             |  |  |  |  |

|           | External Clock Drive                                   | 2-41        |  |  |  |  |

|           | Ordering Information                                   |             |  |  |  |  |

|           | AT90S1300 Register Summary                             |             |  |  |  |  |

|           | AT90S1300 Instruction Set Summary                      | 2-44        |  |  |  |  |

|           |                                                        |             |  |  |  |  |

|           |                                                        |             |  |  |  |  |

| Section 3 | AT90S2312                                              |             |  |  |  |  |

|           | Description                                            | 3-3         |  |  |  |  |

|           | Pin Configuration                                      |             |  |  |  |  |

|           | Block Diagram                                          |             |  |  |  |  |

|           | Pin descriptions                                       |             |  |  |  |  |

|           | AT90S2312 AVR Enhanced RISC Microcontroller CPU        |             |  |  |  |  |

|           | Timer / Counters                                       |             |  |  |  |  |

|           | The Watchdog Timer                                     |             |  |  |  |  |

|           | EEPROM Read/Write Access                               |             |  |  |  |  |

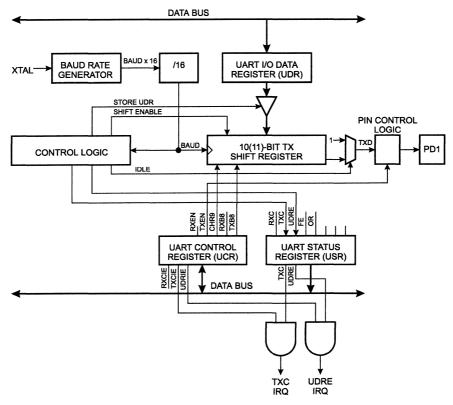

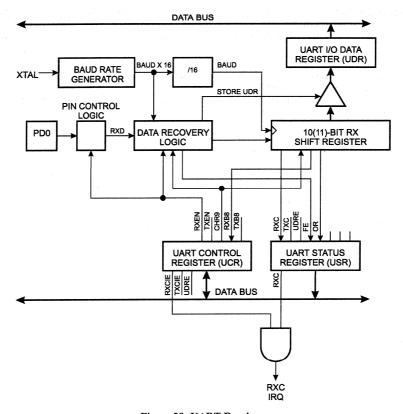

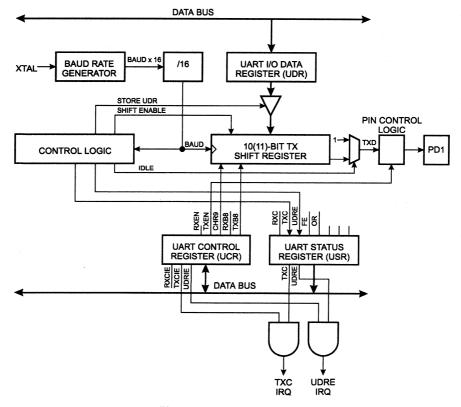

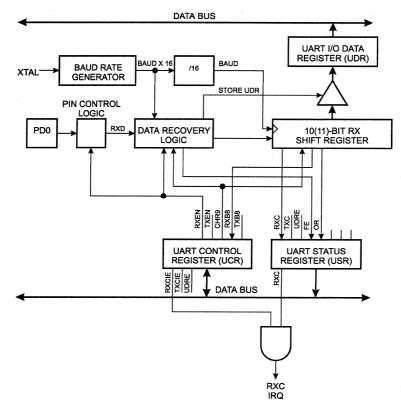

|           | The UART                                               |             |  |  |  |  |

|           | The Analog Comparator                                  |             |  |  |  |  |

|           | I/O-Ports                                              |             |  |  |  |  |

|           | Memory Programming                                     |             |  |  |  |  |

|           | 3                                                      | (continued) |  |  |  |  |

|           |                                                        |             |  |  |  |  |

| Section 3 | A19052312 (Continued)                                |      |

|-----------|------------------------------------------------------|------|

| 5 Y       | Absolute Maximum Ratings                             | 3-62 |

|           | DC Characteristics                                   | 3-62 |

|           | External Clock Drive Waveforms                       | 3-63 |

|           | External Clock Drive                                 | 3-63 |

|           | Ordering Information                                 | 3-64 |

|           | AT90S2312 Register Summary                           | 3-65 |

|           | AT90S2312 Instruction Set Summary                    | 3-66 |

|           |                                                      |      |

|           |                                                      |      |

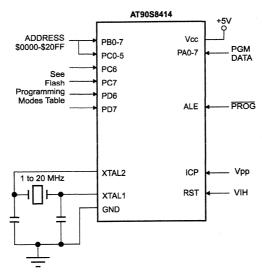

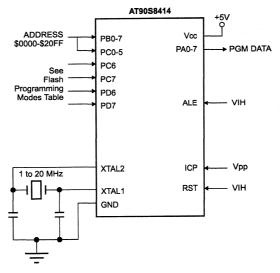

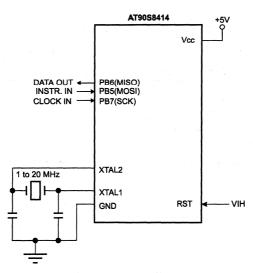

| Section 4 | AT90S8414                                            |      |

| Section 4 |                                                      |      |

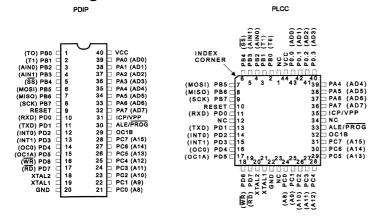

|           | Pin Configurations                                   |      |

|           | Block Diagram                                        |      |

|           | Description                                          |      |

|           | AT90S8414 AVR RISC Microcontroller CPU               |      |

|           | Timer / Counters                                     |      |

|           | The Watchdog Timer                                   |      |

|           | EEPROM Read/Write Access                             |      |

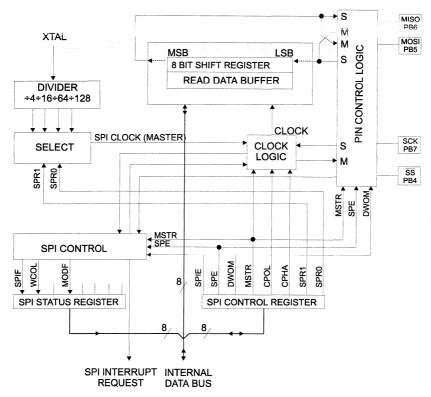

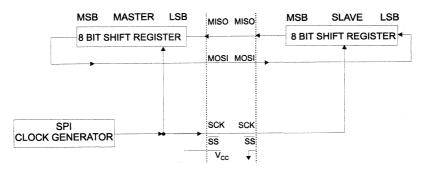

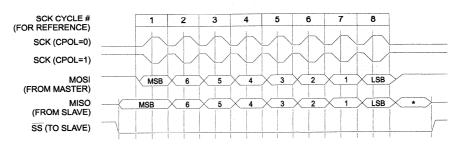

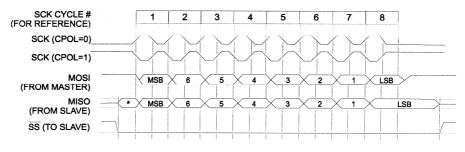

|           | The Serial Peripheral Interface - SPI                |      |

|           | The UART                                             |      |

|           | The Analog Comparator                                |      |

|           | I/O-Ports                                            |      |

|           | Memory Programming                                   |      |

|           | Absolute Maximum Ratings                             |      |

|           |                                                      |      |

|           | AC Characteristics                                   |      |

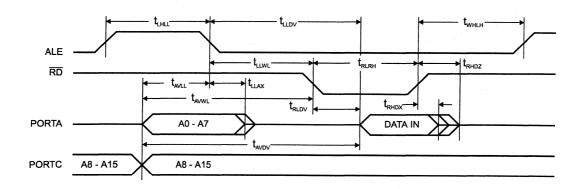

|           | External Data Memory Read Cycle                      |      |

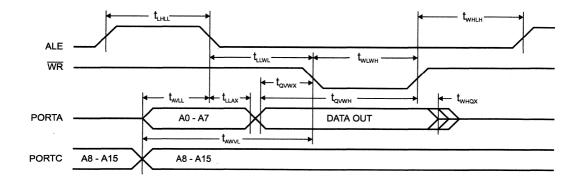

|           | External Memory Write Cycle                          |      |

|           | External Clock Drive Waveforms  External Clock Drive |      |

|           |                                                      |      |

|           | Ordering Information                                 |      |

|           | AT90S8414 Register Summary                           |      |

|           | AT90S8414 Instruction Set Summary                    | 4-84 |

|           |                                                      |      |

|           |                                                      |      |

| Section 5 | Instruction Set                                      |      |

|           | Instruction Set                                      | 5-1  |

|           |                                                      |      |

ii

# Table of Contents

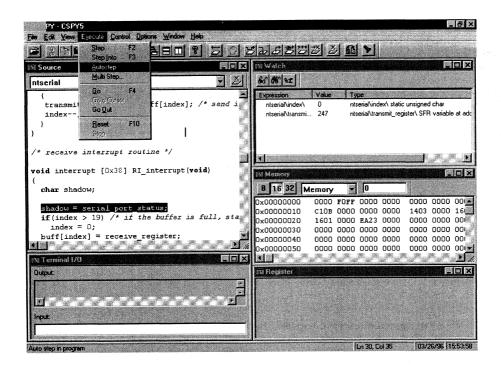

| Section 6 | Development Tools                    |       |      |      |

|-----------|--------------------------------------|-------|------|------|

|           | Development Tools                    |       | <br> | 6-1  |

|           |                                      |       |      |      |

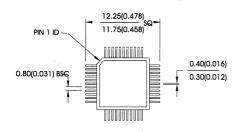

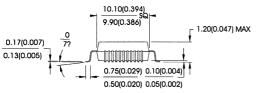

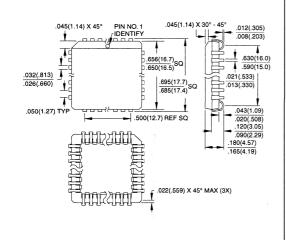

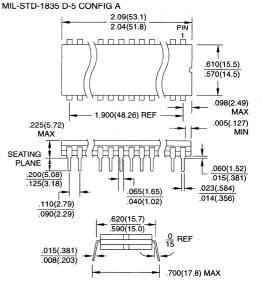

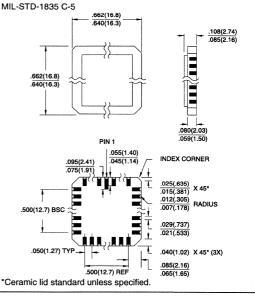

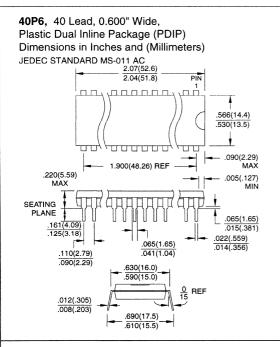

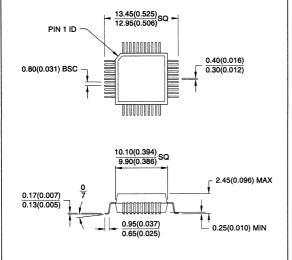

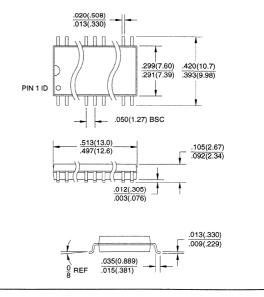

| Section 7 | Package Outlines                     |       |      |      |

|           | Standard Package Outlines            | ••••• | <br> | 7-3  |

|           |                                      |       |      |      |

| Section 8 | Miscellaneous Information            |       |      |      |

|           | Atmel Product Guide                  |       | <br> | 8-3  |

|           | Atmel Sales Offices & Operations     |       | <br> | 8-9  |

|           | Atmel North American Distributors    |       |      |      |

|           | Atmel North American Representatives |       |      |      |

|           | Atmel International Representatives  |       | <br> | 8-25 |

| Overview                 |         |  | 1   |

|--------------------------|---------|--|-----|

|                          |         |  |     |

| AT90S1300                |         |  | 2   |

| 4.7000040                |         |  | 200 |

| AT90S2312                |         |  |     |

| AT90S8414                |         |  | 4   |

| Instruction Set          |         |  | 5   |

| <b>Development Tools</b> |         |  | 6   |

| Package Outlines         |         |  | 7   |

| Miscellaneous Info       | rmation |  |     |

## **AVR™** Enhanced RISC Microcontrollers

Atmel Corporation is a leading manufacturer of a broad range of high performance, low power nonvolatile memory and logic integrated circuits (ICs) that focus on the telecommunications, computer, networking, consumer and automotive markets. Atmel's Flash-based microcontroller families incorporate advanced single voltage Flash memory technology in the industry's broadest line of Flash and EEPROM based products.

With the Flash memory-based microcontrollers from Atmel, you can achieve safe, easy reconfigurability:

- -Change code in seconds, shortening the development cycle

- -Stock just one part

- -Zero scrap due to misprogramming

- -Accelerate product testing

- -Make changes remotely

- -Customize each product on the line

The *AVR* enhanced RISC microcontrollers are based on a new RISC architecture that has been developed to take advantage of semiconductor integration and software capabilities in the 1990's. The resulting microcontrollers offer the highest MIPS/milliwatt capability available in the 8 bit MCU market.

High level languages are rapidly becoming the standard programming methodology for embedded microcontrollers due to improved time-to-market and simplified maintenance support. The *AVR* architecture was developed in conjunction with C language experts to ensure that the hardware and software work hand in hand to develop highly efficient, high performance code.

In order to optimize code size, performance and power consumption, the *AVR* architecture has incorporated a large fast-access register file and fast single-cycle instructions.

The fast-access RISC register file consists of 32 general purpose working resisters. Traditional accumulator based architectures require large amounts of program code for data transfers between the accumulator and memory. With 32 working registers (accumulators) in the *AVR* these data transfers are eliminated.

The *AVR* pre-fetches an instruction during the previous instruction execution and then executes in a single cycle. In other CISC- and RISC-like architectures, the external oscillator clock is divided down (by as much as 12 times) to the traditional internal execution cycle. The *AVR* enhanced RISC microcontrollers execute an instruction in a single clock cycle and are the first true RISC machines in the 8 bit market.

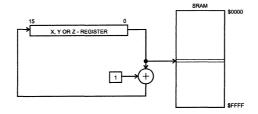

The AVR architecture supports a complete spectrum of price performance from simple small pin count controllers to high range devices with large on-chip memories. The Harvard style architecture directly addresses up to 8M bytes of program memory and 8M bytes of data memory. The register file is dual mapped and can be addressed as part of the on-chip SRAM memory to enable fast context switching.

The *AVR* enhanced RISC microcontroller family is manufactured with Atmel's low-power nonvolatile CMOS technology. The on-chip In-System-Programmable (ISP) downloadable Flash memory allows the program memory to be reprogrammed in system through an SPI serial port or by a conventional memory programmer. By combining an enhanced RISC architecture with downloadable Flash memory on the same chip, the *AVR* family offers a powerful solution to embedded control applications.

| Overview                 |    | 1 |

|--------------------------|----|---|

| AT90S1300                |    | 2 |

|                          |    |   |

| AT90S2312                |    | 3 |

| AT90S8414                |    | 4 |

| Instruction Set          |    | 5 |

| <b>Development Tools</b> |    | 6 |

| Package Outlines         |    | 7 |

| Miscellaneous Informati  | on | 8 |

# **Contents**

| Description                                                           | 2-3  |

|-----------------------------------------------------------------------|------|

| Pin Configuration                                                     | 2-3  |

| Block Diagram                                                         | 2-4  |

| Pin Descriptions                                                      | 2-5  |

| Crystal Oscillator                                                    |      |

| AT90S1300 AVR Enhanced RISC Microcontroller CPU                       |      |

| Architectural Overview                                                |      |

| The General Purpose Register File                                     | 2-8  |

| The ALU - Arithmetic Logic Unit.                                      |      |

| The Downloadable Flash Program Memory                                 |      |

| The Program and Data Addressing Modes                                 |      |

| REGISTER DIRECT, SINGLE REGISTER Rd                                   | 2-9  |

| REGISTER DIRECT, TWO REGISTERS Rd AND Rr                              |      |

| I/O DIRECTRELATIVE PROGRAM ADDRESSING, RJMP AND RCALL                 |      |

| Subroutine and Interrupt Hardware Stack                               |      |

| The EEPROM Data Memory                                                |      |

| Instruction Execution Timing.                                         |      |

| I/O Memory                                                            |      |

| THE STATUS REGISTER - SREG                                            |      |

| Reset and Interrupt Handling                                          |      |

| RESETINTERRUPT HANDLING.                                              |      |

| THE GENERAL INTERRUPT MASK REGISTER - GIMSK                           |      |

| THE TIMER/COUNTER INTERRUPT MASK REGISTER - TIMSK                     | 2-15 |

| THE TIMER/COUNTER INTERRUPT FLAG REGISTER - TIFR                      |      |

| EXTERNAL INTERRUPTS                                                   |      |

| THE MCU CONTROL REGISTER - MCUCR                                      |      |

| Timer / Counter                                                       | 2-17 |

| The Timer/Counter Prescaler                                           | 2-17 |

| The 8-bit Timer/Counter0                                              | 2-17 |

| THE TIMER/COUNTERO CONTROL REGISTER - TCCR0                           |      |

| THE TIMER COUNTER 0 - TCNT0<br>THE OUTPUT COMPARE REGISTER 0 - OCR0   | 2-19 |

| The Watchdog Timer                                                    |      |

| THE WATCHDOG TIMER CONTROL REGISTER - WDTCR                           |      |

|                                                                       |      |

| EEPROM Read/Write Access                                              |      |

| THE EEPROM ADDRESS REGISTER - EEAR<br>THE EEPROM DATA REGISTER - EEDR |      |

| THE EEPROM CONTROL REGISTER - EECR                                    |      |

| The Analog Comparator                                                 |      |

| THE ANALOG COMPARATOR CONTROL AND STATUS REGISTER - ACSR              |      |

|                                                                       |      |

| I/O-Ports                                                             |      |

| Port B. THE PORTB DATA REGISTER - PORTB                               |      |

| THE PORT B DATA DIRECTION REGISTER - DDRB                             |      |

| THE PORT B INPUT PIN ADDRESS - PINB                                   | 2-24 |

| PORTB AS GENERAL DIGITAL I/O                                          |      |

| ALTERNATE FUNCTIONS FOR PORTB                                         |      |

| TORT D SCHEMATICS                                                     |      |

| Port D                                    | 2-28 |

|-------------------------------------------|------|

| THE PORTD DATA REGISTER - PORTD           | 2-20 |

| THE PORT D DATA DIRECTION REGISTER - DDRD | 2-29 |

| THE PORT D INPUT PINS ADDRESS - PIND      | 2-29 |

| PORTD AS GENERAL DIGITAL I/O              |      |

| ALTERNATE FUNCTIONS FOR PORTD             |      |

| PORTD SCHEMATICS                          | 2-30 |

| Memory Programming                        | 2-32 |

| Program Memory Lock Bits                  | 2-32 |

| Programming the Flash and EEPROM          | 2-32 |

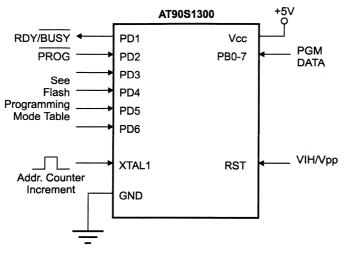

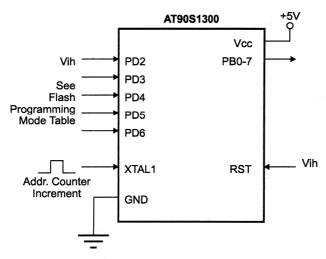

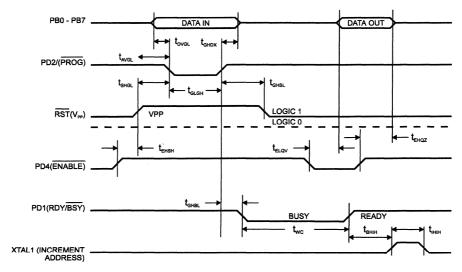

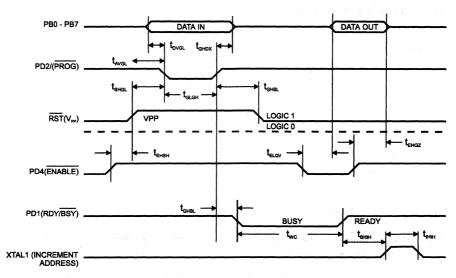

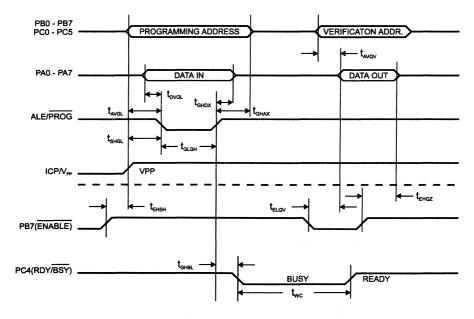

| Parallel Programming                      | 2-33 |

| INTERNAL ADDRESS COUNTER                  |      |

| PARALLEL PROGRAMMING ALGORITHM            |      |

| DATA POLLING                              | 2-33 |

| READY/ BUSY                               | 2-33 |

| PROGRAM VERIFY                            |      |

| CHIP ERASE                                |      |

| READING THE SIGNATURE BYTES               |      |

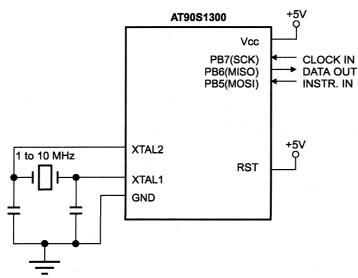

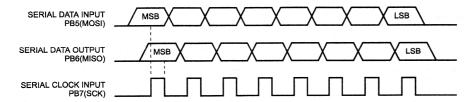

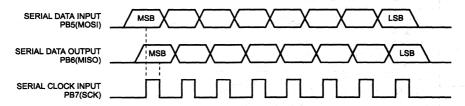

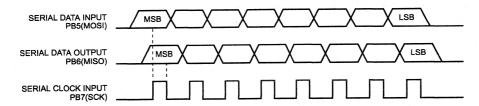

| Serial Downloading                        |      |

| SERIAL PROGRAMMING ALGORITHM              |      |

| Programming Characteristics               | 2-38 |

| Absolute Maximum Ratings                  | 2-39 |

| D.C. Characteristics                      | 2-40 |

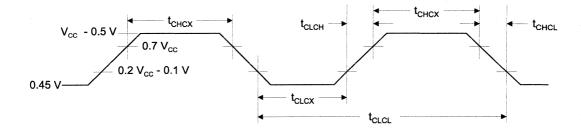

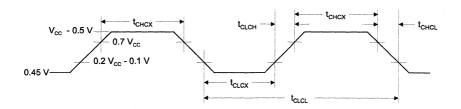

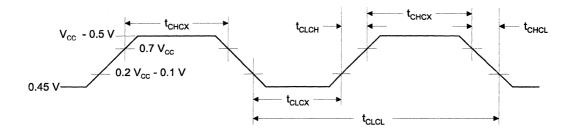

| External Clock Drive Waveforms            | 2-41 |

| External Clock Drive                      | 2-41 |

| Ordering Information                      | 2-42 |

| AT90S1300 Register Summary                | 2-43 |

| AT90S1300 Instruction Set Summary         |      |

|                                           |      |

## **Features**

- Utilizes the AVR™ Enhanced RISC Architecture

- AVR™ High Performance and Low Power RISC Architecture

- 83 Powerful Instructions Most Single Clock Cycle Execution

- 1K bytes of In-System Reprogrammable Downloadable Flash SPI Serial Interface for Program Downloading Endurance: 1,000 Write/Erase Cycles

• 128 bytes EEPROM

Endurance: 100,000 Write/Erase Cycles 32 x 8 General Purpose Working Registers

15 Programmable I/O Lines

VCC Min.: 2.7 VFully Static Operation

- One 8-Bit Timer/Counter with Separate Prescaler

- External and Internal Interrupt Sources

- Programmable Watchdog Timer

- On-Chip Analog Comparator

- Low Power Idle and Power Down Modes

- Programming Lock for Software Security

- 20-Pins Device

# **Description**

The AT90S1300 is a low-power CMOS 8 bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the AT90S1300 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

The AVR core is based on an enhanced RISC architecture that combines a rich instruction set with the 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

(continued)

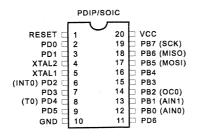

# **Pin Configuration**

8-Bit **AVR**Microcontroller with 1K bytes

Downloadable

Flash

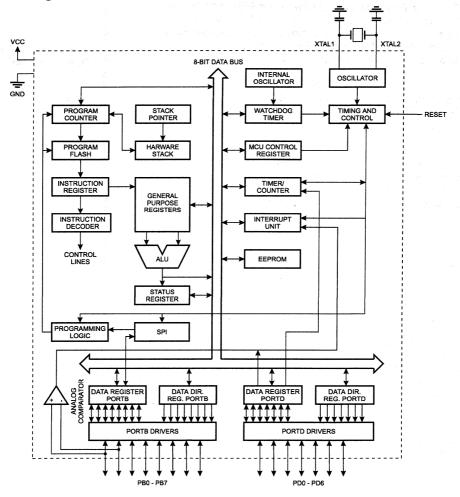

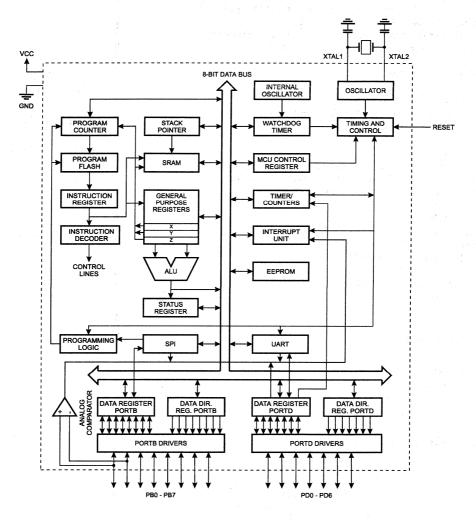

# **Block Diagram**

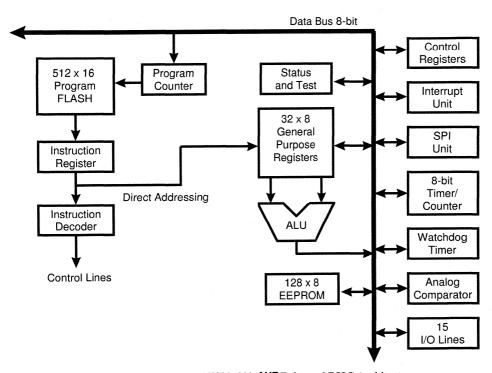

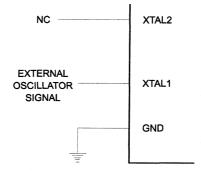

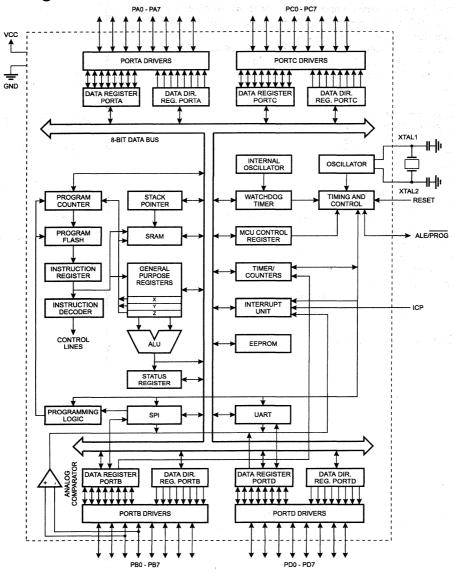

Figure 1: The AT90S1300 Block Diagram

# **Description** (Continued)

The architecture supports high level languages efficiently as well as extremely dense assembler code programs. The AT90S1300 provides the following features: 1K bytes of Downloadable Flash, 128 bytes EEPROM, 15 general purpose I/O lines, 32 general purpose working registers, flexible timer/counter with compare modes, internal and external interrupts, programmable Watchdog Timer with internal oscillator, an SPI serial port for program downloading and two software selectable power saving modes. The Idle Mode stops the CPU while allowing the registers, timer/counter and interrupt system to continue functioning. The power down mode saves the register contents but freezes the oscillator, disabling all other chip functions until the next interrupt or hardware reset.

The device is manufactured using Atmel's high density non-volatile memory technology. The on-chip Downloadable Flash allows the program memory to be reprogrammed in-system through an SPI serial interface or by a conventional nonvolatile memory programmer. By combining an enhanced RISC 8 bit CPU with Downloadable Flash on a monolithic chip, the Atmel AT90S1300 is a powerful microcontroller that provides a highly flexible and cost effective solution to many embedded control applications.

The AT90S1300 AVR is supported with a full suite of program and system development tools including: C compilers, macro assemblers, program debugger/simulators, in-circuit emulators, and evaluation kits.

# **Pin Descriptions**

VCC

Supply voltage pin.

**GND**

Ground pin.

#### Port B (PB7..PB0)

Port B is an 8-bit bi-directional I/O port. Port pins can provide internal pullups (selected for each bit). PB0 and PB1 also serve as the positive input (AIN0) and the negative input (AIN1), respectively, of the on-chip analog comparator. The Port B output buffers can sink 20mA and can drive LED displays directly. When pins PB0 to PB7 are used as inputs and are externally pulled low, they will source current (IIL) if the internal pullups are activated.

Port B also serves the functions of various special features of the AT90S1300 as listed on Page 2-24.

#### Port D (PD6..PD0)

Port D has seven bi-directional I/O pins with internal pullups, PD6. PD0. The Port D output buffers can sink 20 mA. As inputs, Port D pins that are externally pulled low will source current (IIL) if the pullups are activated.

Port D also serves the functions of various special features of the AT90S1300 as listed on Page 2-24.

#### RESET

Reset input. A high on this pin for two machine cycles while the oscillator is running resets the device.

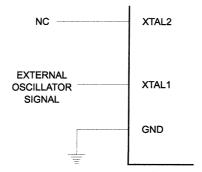

#### XTAL1

Input to the inverting oscillator amplifier and input to the internal clock operating circuit.

#### XTAL2

Output from the inverting oscillator amplifier

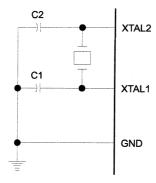

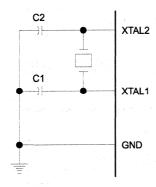

# **Crystal Oscillator**

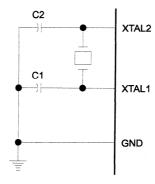

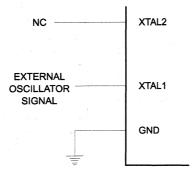

XTAL1 and XTAL2 are input and output, respectively, of an inverting amplifier which can be configured for use as an on-chip oscillator, as shown in Figure 2. Either a quartz crystal or a ceramic resonator may be used. To drive the device from an external clock source, XTAL2 should be left unconnected while XTAL1 is driven as shown in Figure 3.

Figure 2: Oscillator Connections

Figure 3: External Clock Drive Configuration

# AT90S1300 AVR Enhanced RISC Microcontroller CPU

The AT90S1300 AVR RISC microcontroller is upward compatible with the AVR Enhanced RISC Architecture. The programs written for the AT90S1300 MCU are compatible with the range of AVR 8-bit MCUs (AT90Sxxxx) with respect to source code and clock cycles for execution.

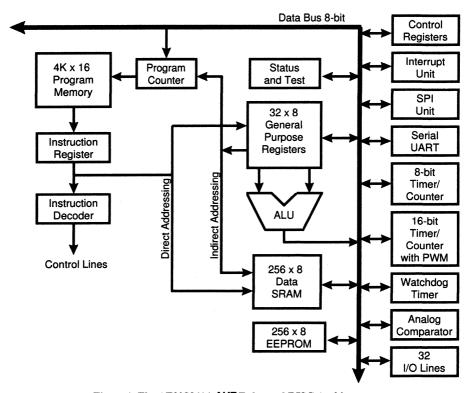

## **Architectural Overview**

The fast-access register file concept contains  $32 \times 8$ -bit general purpose working registers with a single clock cycle access time. This means that during one single clock cycle, one ALU (Arithmetic Logic Unit) operation is executed. Two operands are output from the register file, the operation is executed, and the result is stored back in the register file - in one clock cycle.

# AVR™ AT90S1300 Architecture

Figure 4: The AT90S1300 AVR Enhanced RISC Architecture

The ALU supports arithmetic and logic functions between registers or between a constant and a register. Single register operations are also executed in the ALU. Figure 4 shows the AT90S1300 AVR Enhanced RISC microcontroller architecture. The AVR uses a Harvard architecture concept - with separate memories and buses for program and data

memories. The program memory is accessed with a single level pipelining. While one instruction is being executed, the next instruction is pre-fetched from the program memory. This concept enables instructions to be executed in every clock cycle. The program memory is in-system downloadable Flash memory.

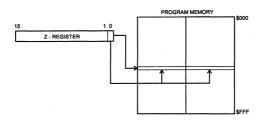

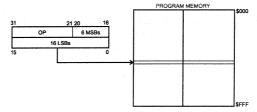

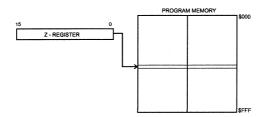

With the relative jump and relative call instructions, the whole 512 address space is directly accessed. All AVR instructions have a single 16-bit word format, meaning that every program memory address contains a single 16-bit instruction.

During interrupts and subroutine calls, the return address program counter (PC) is stored on the stack. The stack is a 4 level deep hardware stack dedicated for subroutines and interrupts.

The I/O memory space contains 64 addresses for CPU peripheral functions as Control Registers, Timer/Counters, A/D-converters, and other I/O functions. The memory spaces in the AVR architecture are all linear and regular memory maps.

A flexible interrupt module has its control registers in the I/O space with an additional global interrupt enable bit in the status register. All the different interrupts have a separate interrupt vector in the interrupt vector table at the beginning of the program memory. The different interrupts have priority in accordance with their interrupt vector position. The lower the interrupt address vector the higher priority.

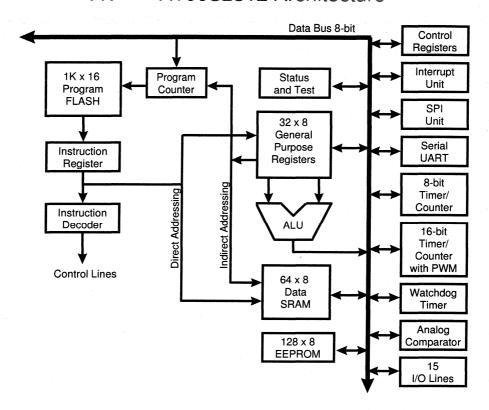

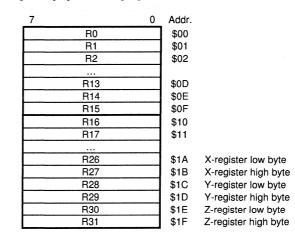

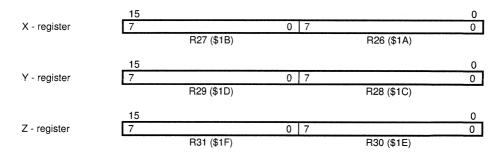

## The General Purpose Register File

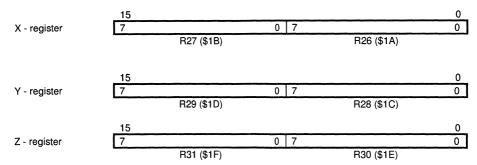

Figure 5 shows the structure of the 32 general purpose registers in the CPU.

|           |     | U |

|-----------|-----|---|

|           | R0  |   |

|           | R1  |   |

|           | R2  |   |

| General   |     |   |

| Purpose   |     |   |

| Working   | R28 |   |

| Registers | R29 |   |

|           | R30 |   |

|           | R31 |   |

|           |     |   |

Figure 5: AVR CPU General Purpose Working Registers

All the register operating instructions in the instruction set have direct and single cycle access to all registers. The only exception is the five constant arithmetic and logic instructions SBCI, SUBI, CPI, ANDI, ORI between a constant and a register and the LDI instruction for load immediate constant data. These instructions apply to the second half of the registers in the register file - R16..R31. The general SBC, SUB, CP, AND, OR and all other operations between two registers or on a single register apply to the entire register file.

# The ALU - Arithmetic Logic Unit

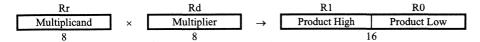

The high-performance AVR ALU operates in direct connection with all the 32 general purpose working registers. Within a single clock cycle, ALU operations between registers in the register file are executed. The ALU operations are divided into three main categories - arithmetic, logic and bit-functions. Some microcontrollers in the AVR product family feature a hardware multiplier in the arithmetic part of the ALU.

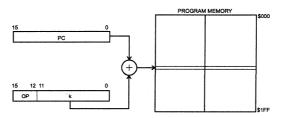

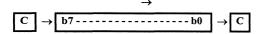

## The Downloadable Flash Program Memory

The AT90S1300 contains 1K bytes on-chip downloadable Flash memory for program storage. Since all instructions are single 16-bit words, the Flash is organized as  $512 \times 16$  words. The Flash memory has an endurance of at least 1000 write/erase cycles.

The AT90S1300 Program Counter is 9 bit wide, thus addressing the 512 words Flash program memory.

See Page 2-32 for a detailed description on Flash data downloading.

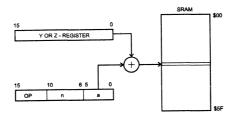

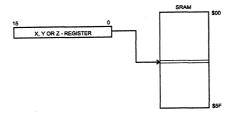

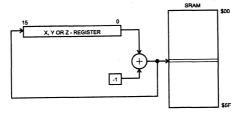

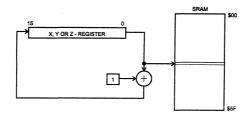

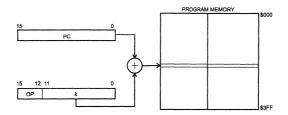

## The Program and Data Addressing Modes

The AT90S1300 AVR Enhanced RISC Microcontroller supports powerful and efficient addressing modes. This section describes the different addressing modes supported in the AT90S1300. In the figures, OP means the operation code part of the instruction word.

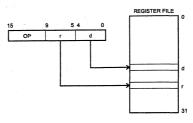

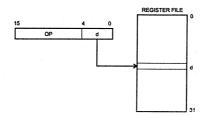

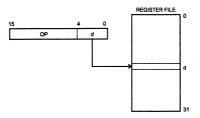

#### REGISTER DIRECT, SINGLE REGISTER Rd

Figure 6: Direct Single Register Addressing

The operand is contained in register d (Rd).

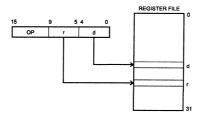

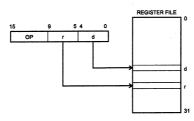

## REGISTER DIRECT, TWO REGISTERS Rd AND Rr

Figure 7: Direct Register Addressing, Two Registers

Operands are contained in register r (Rr) and d (Rd). The result is stored in register d (Rd).

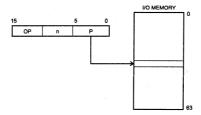

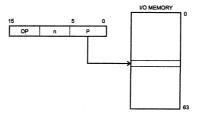

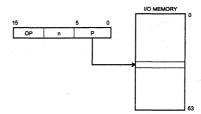

#### I/O DIRECT

Figure 8: I/O Direct Addressing

Operand address is contained in 6 bits of the instruction word. n is the destination or source register address.

#### RELATIVE PROGRAM ADDRESSING, RJMP AND RCALL

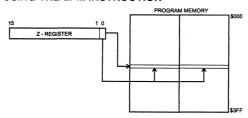

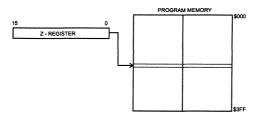

Figure 9: Relative Program Memory Addressing

Program execution continues at address PC + k. The relative address k is in the range from -2K to +(2K - 1).

# **Subroutine and Interrupt Hardware Stack**

The AT90S1300 uses a 4 level deep hardware stack for subroutines and interrupts. The hardware stack is 9 bit wide, and stores the Program Counter - PC - return address while subroutines and interrupts are executed.

RCALL instructions and interrupts push the PC return address onto stack level 0, and the data in the other stack levels 1-3 are pushed one level deeper in the stack. When a RET or RETI instruction is executed the returning PC is fetched from the stack level 0, and the data in the other stack levels 1-3 are popped one level in the stack.

If more than 4 subsequent subroutine calls or interrupts are executed, only the most recent 4 return addresses are stored in the stack.

# **The EEPROM Data Memory**

The AT90S1300 contains 128 bytes of data EEPROM memory. It is organized as a separate data space, in which single bytes can be read and written. The EEPROM has an endurance of at least 100,000 write/erase cycles. The access between the EEPROM and the CPU is described on Page 2-21 specifying the EEPROM address register, the EEPROM data register, and the EEPROM control register. For the SPI data downloading, see Page 2-36 for a detailed description.

## **Instruction Execution Timing**

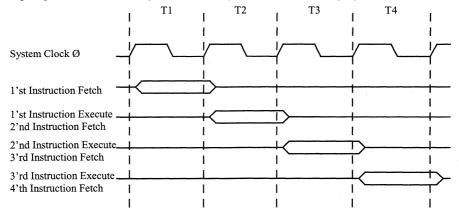

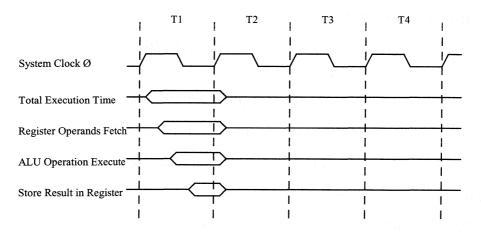

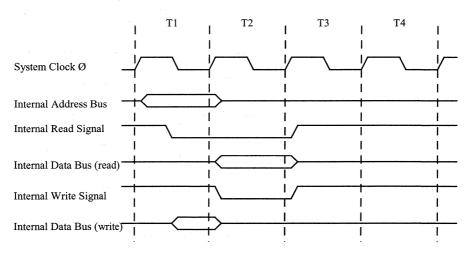

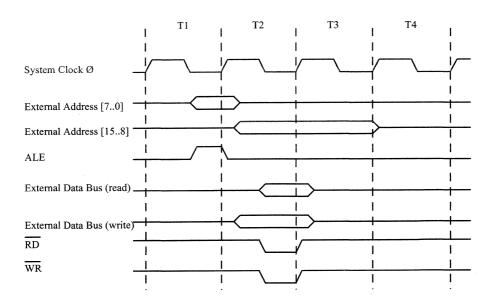

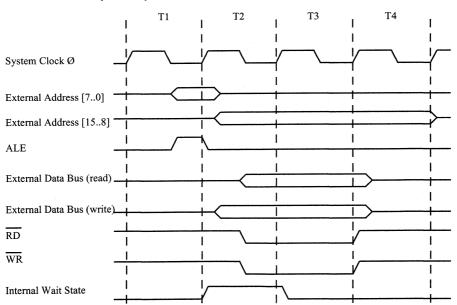

This section describes the general access timing concepts for instruction execution and internal memory access.

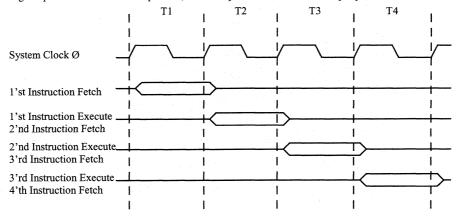

The AVR CPU is driven by the System Clock  $\emptyset$ , directly generated from the external clock crystal for the chip. No internal clock division is used.

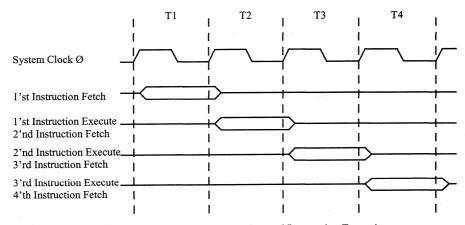

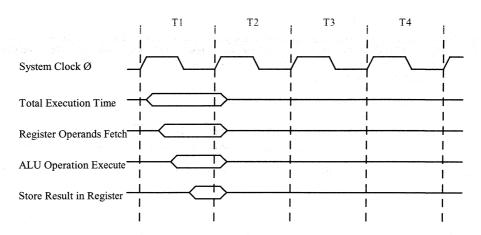

Figure 10 shows the parallel instruction fetches and instruction executions enabled by the Harvard architecture and the fast-access register file concept. This is the basic pipelining concept to obtain up to 1 MIPS per MHz with the corresponding unique results for functions per cost, functions per clocks, and functions per power-unit.

Figure 10: The Parallel Instruction Fetches and Instruction Executions

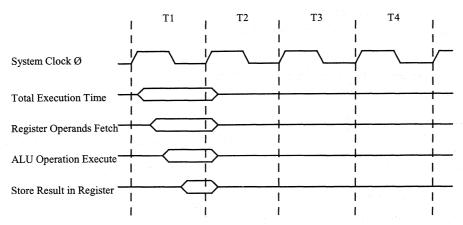

Figure 11 shows the internal timing concept for the register file. In a single clock cycle an ALU operation using two register operands is executed, and the result is stored back to the destination register.

Figure 11: Single Cycle ALU Operation

## I/O Memory

The I/O space definition of the AT90S1300 is shown in the following table:

Table 1: The AT90S1300 I/O Space

| Address Hex | Name  | Function                                      |  |  |  |

|-------------|-------|-----------------------------------------------|--|--|--|

| \$3F        | SREG  | Status REGister                               |  |  |  |

| \$3B        | GIMSK | General Interrupt MaSK register               |  |  |  |

| \$39        | TIMSK | Timer/Counter Interrupt MaSK register         |  |  |  |

| \$38        | TIFR  | Timer/Counter Interrupt Flag register         |  |  |  |

| \$35        | MCUCR | MCU general Control Register                  |  |  |  |

| \$33        | TCCR0 | Timer/Counter 0 Control Register              |  |  |  |

| \$32        | TCNT0 | Timer/Counter 0 (8-bit)                       |  |  |  |

| \$31        | OCR0  | Output Compare Register 0                     |  |  |  |

| \$21        | WDTCR | Watchdog Timer Control Register               |  |  |  |

| \$1E        | EEAR  | EEPROM Address Register                       |  |  |  |

| \$1D        | EEDR  | EEPROM Data Register                          |  |  |  |

| \$1C        | EECR  | EEPROM Control Register                       |  |  |  |

| \$18        | PORTB | Data Register, Port B                         |  |  |  |

| \$17        | DDRB  | Data Direction Register, Port B               |  |  |  |

| \$16        | PINB  | Input Pins, Port B                            |  |  |  |

| \$12        | PORTD | Data Register, Port D                         |  |  |  |

| \$11        | DDRD  | Data Direction Register, Port D               |  |  |  |

| \$10        | PIND  | Input Pins, Port D                            |  |  |  |

| \$08        | ACSR  | Analog Comparator Control and Status Register |  |  |  |

Note: reserved and unused locations are not shown in the table

All the different AT90S1300 I/Os and peripherals are placed in the I/O space. The different I/O locations are accessed by the IN and OUT instructions transferring data between the 32 general purpose working registers and the I/O space. The different I/O and peripherals control registers are explained in the following sections.

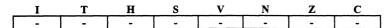

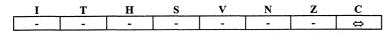

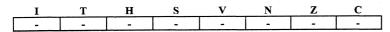

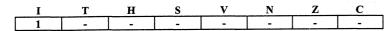

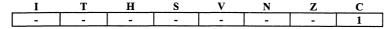

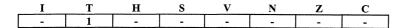

#### THE STATUS REGISTER - SREG

The AVR status register - SREG - at I/O space location \$3F is defined as:

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | _    |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|------|

| \$3F          | ı   | Т   | Н   | S   | ٧   | N   | Z   | С   | SREG |

| Read/Write    | R/W | _    |

| Initial value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |      |

#### Bit 7 - I: Global Interrupt Enable:

The global interrupt enable bit must be set (one) for the interrupts to be enabled. The individual interrupt enable control is then performed in the interrupt mask registers - GIMSK/TIMSK. If the global interrupt enable register is cleared (zero), none of the interrupts are enabled independent of the GIMSK/TIMSK values. The I-bit is cleared by hardware after an interrupt has occurred, and is set by the RETI instruction to enable subsequent interrupts.

#### Bit 6 - T: Bit Copy Storage:

The bit copy instructions BLD (Bit LoaD) and BST (Bit STore) use the T bit as source and destination for the operated bit. A bit from a register in the register file can be copied into T by the BST instruction, and a bit in T can be copied into a bit in a register in the register file by the BLD instruction.

#### Bit 5 - H: Half Carry Flag:

The half carry flag H indicates a half carry in some arithmetic operations. See the Instruction Set Description for detailed information.

#### Bit 4 - S: Sign Bit, $S = N \oplus V$ :

The S-bit is always an exclusive or between the negative flag N and the two's complement overflow flag V. See the Instruction Set Description for detailed information.

#### Bit 3 - V: Two's Complement Overflow Flag:

The two's complement overflow flag V supports two's complement arithmetics. See the Instruction Set Description for detailed information.

#### Bit 2 - N: Negative Flag:

The negative flag  $\bar{N}$  indicates a negative result after the different arithmetic and logic operations. See the Instruction Set Description for detailed information.

#### Bit 1 - Z: Zero Flag:

The zero flag Z indicates a zero result after the different arithmetic and logic operations. See the Instruction Set Description for detailed information.

#### Bit 0 - C: Carry Flag:

The carry flag C indicates a carry in an arithmetic or logic operation. See the Instruction Set Description for detailed information.

## **Reset and Interrupt Handling**

The AT90S1300 provides 4 different interrupt sources. These interrupts and the separate reset vector, each have a separate program vector in the program memory space. All the interrupts are assigned individual enable bits which must be set (one) together with the I-bit in the status register in order to enable the interrupt.

The lowest addresses in the program memory space are automatically defined as the Reset and Interrupt vectors. The complete list of vectors is shown in Table 2: Reset and Interrupt Vectors. The list also determines the priority levels of the different interrupts. The lower the address the higher is the priority level. RESET has the highest priority, and next is INTO - the External Interrupt Request 0 etc.

**Table 2: Reset and Interrupt Vectors**

| Vector No. | Program Address<br>\$000 | Source<br>RESET | Interrupt Definition Hardware Pin and Watchdog Reset |

|------------|--------------------------|-----------------|------------------------------------------------------|

| 2          | \$001                    | INT0            | External Interrupt Request 0                         |

| 3          | \$002                    | TIMER0, COMP0   | Timer/Counter0 Compare Match                         |

| 4          | \$003                    | TIMER0, OVF0    | Timer/Counter0 Overflow                              |

| 5          | \$004                    | ANA_COMP        | Analog Comparator                                    |

The most typical and general program setup for the Reset and Interrupt Vector Addresses are:

| Address | Labels | Code                | Comments                   |

|---------|--------|---------------------|----------------------------|

| \$000   |        | rjmp RESET          | ; Reset handle             |

| \$001   |        | rjmp EXT_INTO       | ; IRQ0 handle              |

| \$002   |        | rjmp TIMO_COMP      | ; Timer0 comp. Handle      |

| \$003   |        | rjmp TIMO_OVF       | ; Timer0 overflow handle   |

| \$004   |        | rjmp ANA_COMP       | ; Analog Comparator Handle |

| ;       |        |                     |                            |

| \$005   | MAIN:  | <instr> xxx</instr> | ; Main program start       |

|         |        |                     |                            |

#### RESET

A Reset State is enabled by a high level on the RESET pin. The pin must be held high for at least two crystal clock cycles. All internal registers are then set to their initial values, and the program starts execution from address \$000. The instruction placed in address \$000 must be a RJMP - relative jump - instruction to the reset handling routine. If the program never enables an interrupt source, the interrupt vectors are not used, and regular program code can be placed at these locations.

#### INTERRUPT HANDLING

The AT90S1300 has two Interrupt Mask control registers GIMSK - General Interrupt MaSK register - at I/O space address \$3B and the TIMSK - Timer/Counter Interrupt MaSK register at I/O address \$39.

When an interrupt occurs, the Global Interrupt Enable I-bit is cleared (zero) and all interrupts are disabled. The user software can set (one) the I-bit to enable interrupts. The I-bit is set (one) when a Return from Interrupt instruction - RETI - is executed.

For Interrupts triggered by events that can remain static (E.g. the Output Compare register0 matching the value of Timer/Counter0) the interrupt flag is set when the event occurs. If the interrupt flag is cleared and the interrupt condition persists, the flag will not be set until the event occurs the next time.

When the Program Counter is vectored to the actual interrupt vector in order to execute the interrupt handling routine, hardware clears the corresponding flag that generated the interrupt. Some of the interrupt flags can also be cleared by writing a logic one to the flag bit position(s) to be cleared.

#### THE GENERAL INTERRUPT MASK REGISTER - GIMSK

| Bit           | 7 | 6    | 5 | 4 | 3 | 2 | 1 | 0 |          |

|---------------|---|------|---|---|---|---|---|---|----------|

| \$3B          | - | INT0 |   | - | • | - | - | - | GIMSK    |

| Read/Write    | R | R/W  | R | R | R | R | R | R | <b>-</b> |

| Initial value | 0 | 0    | 0 | 0 | 0 | 0 | 0 | 0 |          |

#### Bit 7 - Res: Reserved bit:

This bit is a reserved bit in the AT90S1300 and always read zero.

#### Bit 6 - INTO: External Interrupt Request 0 Enable:

When the INT0 bit is set (one) and the I-bit in the Status Register (SREG) is set (one), the external pin interrupt is activated. The Interrupt Sense Control0 bit 1/0 (ISC01 and ISC00) in the MCU general Control Register (MCUCR) defines whether the external interrupt is activated on rising or falling edge of the INT0 pin or level sensed. If the INT0 pin for external interrupts shall be activated, the DDD2 bit in the Data Direction Register PORTD (DDRD) must be cleared (zero) to force an input pin. See also "External Interrupts".

#### Bits 5..0 - Res: Reserved bits:

These bits are reserved bits in the AT90S1300 and always read as zero.

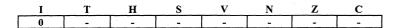

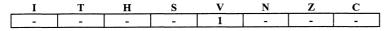

#### THE TIMER/COUNTER INTERRUPT MASK REGISTER - TIMSK

| Bit           | 7 | 6 | 5 | 4 | 3 | 2 | 1     | 0     | _     |

|---------------|---|---|---|---|---|---|-------|-------|-------|

| \$39          | - |   | - |   | - | • | TOIE0 | OCIE0 | TIMSK |

| Read/Write    | R | R | R | R | R | R | R/W   | R/W   | _     |

| Initial value | 0 | 0 | 0 | 0 | 0 | 0 | 0     | 0     |       |

#### Bits 7..2 - Res: Reserved bits:

These bits are reserved bits in the AT90S1300 and always read zero.

#### Bit 1 - TOIE0: Timer/Counter0 Overflow Interrupt Enable:

When the TOIE0 bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter0 Overflow interrupt is enabled. The corresponding interrupt (at vector \$003) is executed if an overflow in Timer/Counter0 occurs. The Overflow Flag (Timer0) is set (one) in the Timer/Counter Interrupt Flag Register - TIFR.

#### Bit 0 - OCIE0 : Timer/Counter0 Output Compare Match Interrupt Enable:

When the OCIE0 bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter0 Compare Match interrupt is enabled. The corresponding interrupt (at vector \$002) is executed if a compare match in Timer/Counter0 occurs. The Compare Flag (Timer0) is set (one) in the Timer/Counter Interrupt Flag Register - TIFR.

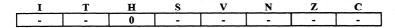

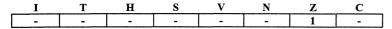

#### THE TIMER/COUNTER INTERRUPT FLAG REGISTER - TIFR

| Bit           | 7 | 6 | 5 | 4 | 3 | 2   | 1    | 0    | _    |

|---------------|---|---|---|---|---|-----|------|------|------|

| \$38          | - | - | - | - |   | -   | TOV0 | OCF0 | TIFR |

| Read/Write    | R | R | R | R | R | R   | R/W  | R/W  | _    |

| Initial value | 0 | 0 | 0 | 0 | 0 | 0 1 | 0    | 0    |      |

#### Bits 7..2 - Res: Reserved bits:

These bits are reserved bits in the AT90S1300 and always read zero.

## Bit 1 - TOV0: Timer/Counter0 Overflow Flag:

The bit TOV0 is set (one) when an overflow occurs in Timer/Counter0. TOV0 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, TOV0 is cleared by writing a logic one to the flag. When the SREG I-bit, and TOIE0 (Timer/Counter0 Overflow Interrupt Enable), and TOV0 are set (one), the Timer/Counter0 Overflow interrupt is executed.

#### Bit 0 - OCF0: Output Compare Flag 0:

The OCF0 bit is set (one) when a compare match occurs between the Timer/Counter0 and the compared data in OCR0 - Output Compare Register0. OCF0 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCF0 is cleared by writing a logic one to the flag.. When the SREG I-bit, and OCIE0 (Timer/Counter0 Compare match Interrupt Enable), and OCF0 are set (one), the Timer/Counter0 Compare match Interrupt is executed.

#### **EXTERNAL INTERRUPTS**

The external interrupts are triggered by the INT0 pin. Since this pin is an alternate function pin in the general I/O ports, the corresponding pin must be set as an input pin in the data direction register - DDRX.

The external interrupt is set up as indicated in the specification for the general interrupt mask register - GIMSK.

#### INTERRUPT RESPONSE TIME

The interrupt execution response times for all the enabled  $AVR^{TM}$  interrupts are 4 clock cycles. After the 4 clock cycles the program vector address for the actual interrupt handling routine is executed. During this 4 clock cycle period, the Program Counter (9 bits) is pushed onto the Stack.

A return from an interrupt handling routine takes 4 clock cycles. During these 4 clock cycles, the Program Counter (9 bits) is popped back from the Stack.

Note that the Status Register - SREG - is not handled by the  $AVR^{TM}$  hardware, neither for interrupts nor for subroutines. For the routines requiring a storage of the SREG, this must be performed by user software.

Note that the Subroutine and Interrupt Stack is a 4 level true hardware stack, and if more than 4 nested subroutines and interrupts are executed, only the most recent 4 return addresses are stored.

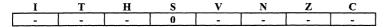

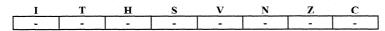

#### THE MCU CONTROL REGISTER - MCUCR

The MCU Control Register contains general microcontroller control bits for general MCU control functions.

| Bit           | 7   | 6 | 5   | 4   | 3 | 2 | 1     | 0     |       |

|---------------|-----|---|-----|-----|---|---|-------|-------|-------|

| \$35          | -   | - | SE  | SM  |   | - | ISC01 | ISC00 | MCUCR |

| Read/Write    | R   | R | R/W | R/W | R | R | R/W   | R/W   | •     |

| Initial value | 0 1 | 0 | 0   | 0   | 0 | 0 | 0     | 0     |       |

#### Bits 7, 6 - Res: Reserved bits:

These bits are reserved bits in the AT90S1300 and always read zero.

#### Bit 5 - SE : Sleep Enable:

The SE bit must be set (one) to make the MCU enter the sleep mode when the SLEEP instruction is executed. To avoid the MCU entering the sleep mode unless it is the programmers purpose, it is recommended to set the Sleep Enable SE bit just before the execution of the SLEEP instruction.

#### Bit 4 - SM : Sleep Mode:

This bit selects between the two available sleep modes - the Idle Mode and the Power Down Mode.

To enter the sleep modes, the SE bit must be set (one) and a SLEEP instruction must be executed. The instruction following SLEEP is executed before entering sleep mode. If an enabled interrupt occurs while the MCU is in a sleep mode, the MCU awakes, executes the interrupt routine and resumes execution from the address following the last executed instruction. If reset occurs while the MCU is in Sleep Mode, the MCU awakes and executes from the reset vector.

When the SM bit is cleared (zero), the SLEEP instruction forces the MCU into the Idle Mode stopping the CPU but allowing the General Purpose Working Registers, Timer/Counters, SPI port, and the interrupt system to continue operating.

When the SM bit is set (one), the SLEEP instruction forces the MCU into the Power Down Mode saving the General Purpose Working Registers, but freezing the oscillator, disabling all other chip functions until the next interrupt or hardware reset.

#### Bits 3, 2 - Res: Reserved bits:

These bits are reserved bits in the AT90S1300 and always read zero.

#### Bits 1, 0 - ISC01, ISC00: Interrupt Sense Control 0 bit 1 and bit 0:

The External Interrupt 0 is activated by the external pin INT0 if the SREG I-flag and the corresponding interrupt mask in the GIMSK register is set. The level and edges on the external INT0 pin that activate the interrupt are defined as:

Table 3: Interrupt 0 Sense Control

|   | ISC01 | ISC00 | Description                                              |

|---|-------|-------|----------------------------------------------------------|

| - | 0     | 0     | The low level of INT0 generates an interrupt request.    |

| - | 0     | 1     | Reserved                                                 |

| - | 1     | 0     | The falling edge of INT0 generates an interrupt request. |

|   | 1     | 1     | The rising edge of INT0 generates an interrupt request.  |

Note: When changing the ISC10/ISC00 bits, INT0 must be disabled by clearing its Interrupt Enable bit in the GIMSK Register. Otherwise an interrupt can occur when the bits are changed.

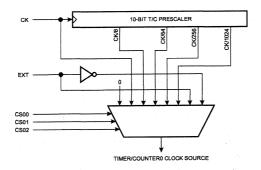

## Timer / Counter

The AT90S1300 provides one general purpose 8-bit Timer/Counter. The Timer/Counter has prescaling selection from the 10-bit prescaling timer. The Timer/Counter can either be used as a timer with an internal clock timebase or as a counter with an external pin connection which triggers the counting.

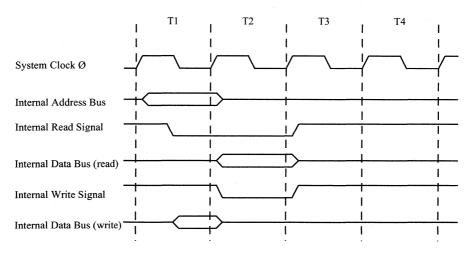

## The Timer/Counter Prescaler

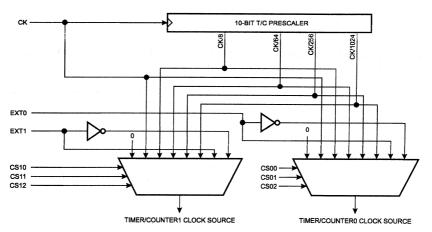

Figure 12 shows the general Timer/Counter prescaler.

Figure 12: Timer/Counter0 Prescaler

The four different prescaled selections are: CK/8, CK/64, CK/256 and CK/1024 where CK is the oscillator clock. For the Timer/Counter, added selections as CK, external source and stop, can be selected as clock sources.

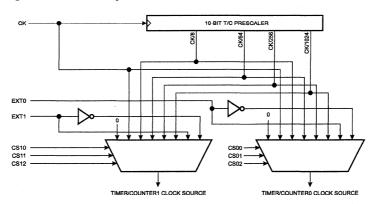

## The 8-bit Timer/Counter0

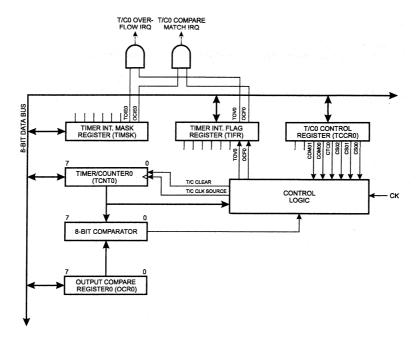

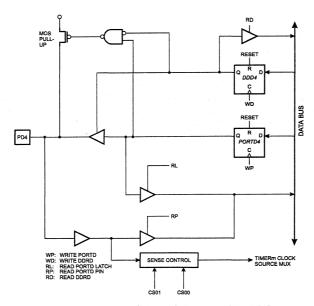

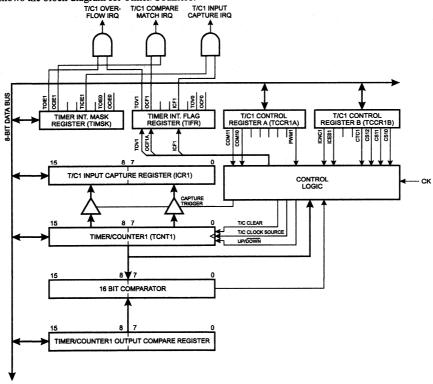

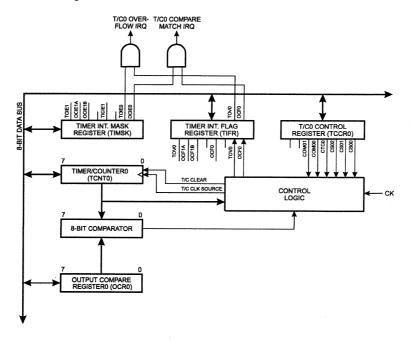

Figure 13 shows the block diagram for Timer/Counter0.

Figure 13: Timer/Counter 0 Block Diagram

The 8-bit Timer/Counter0 can select clock source from CK, prescaled CK, or an external pin. In addition it can be stopped as described in the specification for the Timer/Counter0 Control Register - TCCR0. The different status flags (overflow and compare match) are found in the Timer/Counter Interrupt Flag Register - TIFR. Control signals are found in the Timer/Counter0 Control Register - TCCR0. The interrupt enable/disable settings for Timer/Counter0 are found in the Timer/Counter Interrupt Mask Register - TIMSK.

When Timer/Counter0 is externally clocked, the external signal is synchronized with the oscillator frequency of the CPU. To assure proper sampling of the external clock, the minimum time for the external clock being low and high must be at least one internal CPU clock period. The external clock signal is sampled on the rising edge of the internal CPU clock.

The 8-bit Timer/Counter0 features both a high resolution and a high accuracy usage with the lower prescaling opportunities. Similarly, the high prescaling opportunities make the Timer/Counter0 useful for lower speed functions or exact timing functions with infrequent actions.

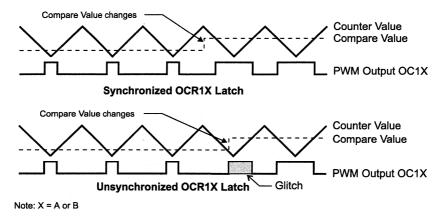

The Timer/Counter0 supports an Output Compare function using the Output Compare Register 0 - OCR0 as the data source to be compared to the Timer/Counter0 contents. The Output Compare functions include optional clearing of the counter on compare matches, and actions on the Output Compare pin 0 on compare matches. The Output Compare pin 0 function makes the Timer/Counter0 useful for PWM (Pulse Width Modulation) functions.

#### THE TIMER/COUNTERO CONTROL REGISTER - TCCRO

| Bit           | 7 | 6 | 5     | 4     | 3    | 2    | 1    | 0    |       |

|---------------|---|---|-------|-------|------|------|------|------|-------|

| \$33          | - | - | COM01 | COM00 | CTC0 | CS02 | CS01 | CS00 | TCCR0 |

| Read/Write    | R | R | R/W   | R/W   | R/W  | R/W  | R/W  | R/W  |       |

| Initial value | 0 | 0 | 0     | 0     | 0    | 0    | 0    | 0    |       |

#### Bits 7,6 - Res: Reserved bits:

These bits are reserved bits in the AT90S1300 and always read zero.

#### Bits 5,4 - COM01, COM00: Compare Output Mode0, bit 1 and 0:

The COM01 and COM00 control bits determine any output pin action following a compare match in Timer/Counter0. Any output pin actions are effective on pin OC0 - Output Compare pin 0. Since this is an alternative function to an I/O port, the corresponding data direction control bit must be set (one) to control an output pin. The control configuration is defined in the following table:

Table 4: Compare 0 Mode Select

| COM01 | COM00 | Description                                      |

|-------|-------|--------------------------------------------------|

| 0     | 0     | Timer/Counter0 disconnected from output pin OC0. |

| 0     | 1 1   | Toggle the OC0 output line.                      |

| 1     | 0     | Clear the OC0 output line (to zero).             |

| 1     | 1     | Set the OC0 output line (to one).                |

Note: When changing the COM01/COM00 bits, Output Compare Interrupt 0 must be disabled by clearing its Interrupt Enable bit in the TIMSK Register. Otherwise an interrupt can occur when the bits are changed.

#### Bit 3 - CTC0: Clear Timer/Counter0 on Compare match:

When the CTC0 control bit is set (one), the Timer/Counter0 is reset to \$00 in the clock cycle after the compare match. If the CTC0 control bit is cleared, the Timer/Counter0 continues running freely until it is stopped, set, cleared or wraps around (overflow).

#### Bits 2,1,0 - CS02, CS01, CS00: Clock Select0, bit 2,1 and 0:

The Clock Select0 bits 2,1 and 0 define the prescaling source of Timer0.

Table 5: Clock 0 Prescale Select

| CS02 | CS01 | CS00 | Description                          |

|------|------|------|--------------------------------------|

| 1 0  | 0    | l 0  | Stop, the Timer/Counter0 is stopped. |

| 0    | 0    | 1    | CK                                   |

| 1 0  | 1    | 0    | CK / 8                               |

| 1 0  | 1    | 1    | CK / 64                              |

| 1    | 0    | 0    | CK / 256                             |

| 1 1  | 0    | 1    | CK / 1024                            |

| 1    | . 1  | 0    | External Pin T0, rising edge         |

| 1 1  | 1    | 1    | External Pin T0, falling edge        |

The Stop condition provides a Timer Enable/Disable function. The CK down divided modes are scaled directly from the CK oscillator clock. If the external pin modes are used, the corresponding setup must be performed in the actual data direction control register (cleared to zero gives an input pin).

#### Bits 5..3 - Res: Reserved bits:

These bits are reserved bits in the AT90S1300 and always read zero.

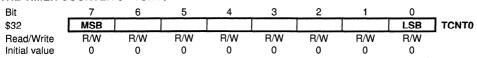

#### THE TIMER COUNTER 0 - TCNT0

The Timer/Counter0 is realized as an up-counter with read and write access. If the Timer/Counter0 is written and a clock source is present, the Timer/Counter0 continues counting in the clock cycle following the write operation.

#### THE OUTPUT COMPARE REGISTER 0 - OCR0

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |      |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|------|

| \$31          | MSB |     |     |     |     |     |     | LSB | OCR0 |

| Read/Write    | R/W |      |

| Initial value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |      |

The Output Compare Register 0 is the source register for the Timer/Counter0 compare match functions.

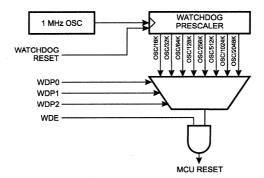

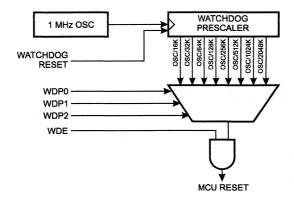

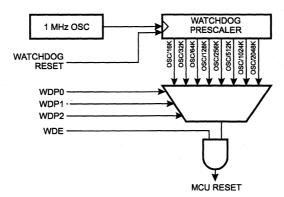

# The Watchdog Timer

The Watchdog Timer is clocked from a separate on-chip oscillator which runs at 1MHz. By controlling the Watchdog Timer prescaler, the Watchdog reset interval can be adjusted from 16 to 2048 ms. The WDR - Watchdog Reset instruction resets the Watchdog Timer. Eight different clock cycle periods can be selected to determine the maximum period between two WDR instructions to avoid that the Watchdog Timer resets the MCU. If the reset period expires without another WDR instruction, the AT90S1300 resets and executes from the reset vector.

Figure 14: Watchdog Timer

#### THE WATCHDOG TIMER CONTROL REGISTER - WDTCR

| Bit           | 7 | 6 | 5 | 4 | 3   | 2    | . 1  | 0    | _     |

|---------------|---|---|---|---|-----|------|------|------|-------|

| \$21          | - | - | - | - | WDE | WDP2 | WDP1 | WDP0 | WDTCR |

| Read/Write    | R | R | R | R | R/W | R/W  | R/W  | R/W  | _     |

| Initial value | 0 | 0 | 0 | 0 | 0   | 0    | 0    | 0    |       |

#### Bits 7..4 - Res: Reserved bits:

These bits are reserved bits in the AT90S1300 and will always read as zero.

#### Bit 3 - WDE: Watchdog Enable:

When the WDE is set (one) the Watchdog Timer is enabled, and if the WDE is cleared (zero) the Watchdog Timer function is disabled.

## Bits 2..0 - WDP2..0: Watchdog Timer Prescaler 2,1 and 0:

The WDP2..0 determine the Watchdog Timer prescaling when the Watchdog Timer is enabled. The different prescaling values and their corresponding Timeout Periods are shown in Table 6.

**Table 6: Watchdog Timer Prescale Select**

| WDP2 | WDP1 | WDP0 | Timeout Period |

|------|------|------|----------------|

| WDFZ | WDF  | WDFU |                |

| 0    | 0    | 0    | 16 ms          |

| 0    | 0    | 1    | 32 ms          |

| 0    | 1    | 0    | 64 ms          |

| 0    | 1    | 1    | 128 ms         |

| 1    | 0    | 0    | 256 ms         |

| 1    | 0    | 1    | 512 ms         |

| 1    | 1    | 0    | 1024 ms        |

| 1    | 1    | 1 1  | 2048 ms        |

# **EEPROM Read/Write Access**

The EEPROM access registers are accessible in the I/O space using the IN and OUT instructions.

The write access time is in the range of 2.5 - 4ms, depending on the Vcc voltages. A self-timing function, however, lets the user software detect when the next byte can be written.

The read access time is the same as for the Flash memory and is of no concern to the user software.

#### THE EEPROM ADDRESS REGISTER - EEAR

| Bit           | 7 | 6   | 5   | 4   | 3   | 2   | 1   | 0   |      |

|---------------|---|-----|-----|-----|-----|-----|-----|-----|------|

| \$1E          | - | MSB |     |     |     |     |     | LSB | EEAR |

| Read/Write    | R | R/W |      |

| Initial value | 0 | 0   | 0   | 0   | 0   | 0   | 0   | 0   |      |

#### Bit 7 - Res: Reserved bit:

This bit is a reserved bit in the AT90S1300 and will always read as zero.

#### Bits 6..0 - EEAR6..0: EEPROM Address:

The EEPROM Address Register - EEAR6..0 - specifies the EEPROM address in the 128 bytes EEPROM space. The EEPROM data bytes are addressed linearly between 0 and 127.

#### THE EEPROM DATA REGISTER - EEDR

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | _    |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|------|

| \$1D          | MSB |     |     |     |     |     |     | LSB | EEDR |

| Read/Write    | R/W |      |

| Initial value | 0   | 0 ; | 0   | 0   | 0   | 0   | 0   | 0   |      |

#### Bits 7..0 - EEDR7..0: EEPROM Data:

For the EEPROM write operation, the EEDR register contains the data to be written to the EEPROM in the address given by the EEAR register. For the EEPROM read operation, the EEDR contains the data read out from the EEPROM at the address given by EEAR.

#### THE EEPROM CONTROL REGISTER - EECR

| Bit           | 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0    | _    |

|---------------|---|---|---|---|---|---|------|------|------|

| \$1C          |   | - | - | - | - |   | EEWE | EERE | EECR |

| Read/Write    | R | R | R | R | R | R | R/W  | R/W  |      |

| Initial value | 0 | 0 | 0 | 0 | 0 | 0 | . 0  | 0    |      |

#### Bits 7..2 - Res: Reserved bits:

These bits are reserved bits in the AT90S1300 and will always be read as zero.

#### Bit 1 - EEWE: EEPROM Write Enable:

The EEPROM Write Enable Signal EEWE is the write strobe to the EEPROM. When address and data are correctly set up, the EEWE bit must be set to write the value into the EEPROM. When the write access time (typically 2.5ms at Vcc=5V and 4ms at Vcc=2.7V) has elapsed, the EEWE bit is cleared (zero) by hardware. The user software can poll this bit and wait for a zero before writing the next byte.

#### Bit 0 - EERE: EEPROM Read Enable:

The EEPROM Read Enable Signal EERE is the read strobe to the EEPROM. When the correct address is set up in the EEAR register, the EERE bit must be set. When the EERE bit is cleared (zero) by hardware, requested data is found in the EEDR register. The EEPROM read access time is within a single clock cycle and there is no need to poll the EERE bit.

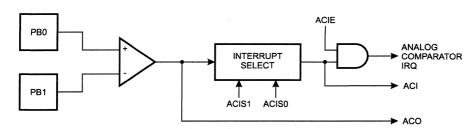

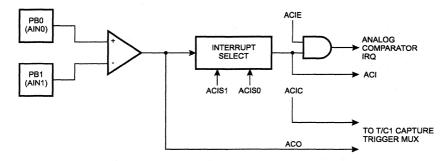

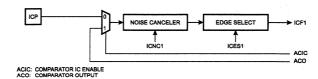

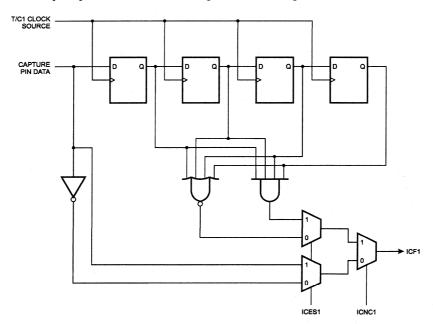

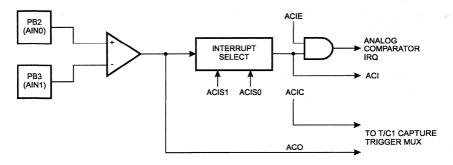

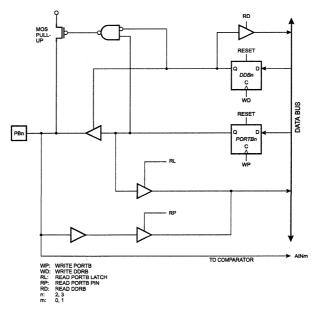

# The Analog Comparator

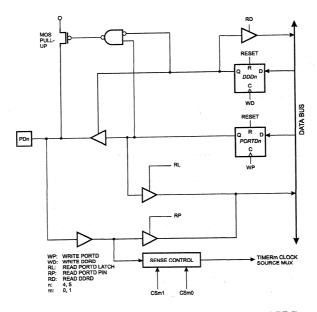

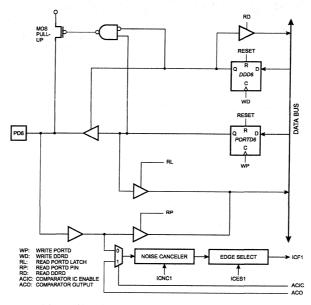

The analog comparator compares the input values on the positive pin PB0 (AIN0) and the negative pin PB1 (AIN1). When the voltage on the positive pin PB0 (AIN0) is higher than the voltage on the negative pin PB1 (AIN1), the Analog Comparator Output, ACO is set (one). The comparator's output can be set to trigger the Analog Comparator interrupt. The user can select Interrupt triggering on comparator output rise, fall or toggle. A block diagram of the comparator and its surrounding logic is shown in Figure 15.

Figure 15: Analog Comparator Block Diagram

#### THE ANALOG COMPARATOR CONTROL AND STATUS REGISTER - ACSR

| Bit           | 7 | 6 | 5   | 4   | 3    | 2    | 1     | 0     |              |

|---------------|---|---|-----|-----|------|------|-------|-------|--------------|

| \$08          | - | - | ACO | ACI | ACIE | ACIC | ACIS1 | ACIS0 | ACSR         |

| Read/Write    | R | R | R   | R/W | R/W  | R/W  | R/W   | R/W   | <del>-</del> |

| Initial value | 0 | 0 | 0   | 0   | 0    | 0    | 0     | 0     |              |

#### Bits 7..6 - Res: Reserved bits:

These bits are reserved bits in the AT90S1300 and will always read as zero.

## Bit 5 - ACO: Analog Comparator Output:

ACO is directly connected to the comparator output.

#### Bit 4 - ACI: Analog Comparator Interrupt Flag:

This bit is set (one) when a comparator output event triggers the interrupt mode defined by ACI1 and ACI0. The Analog Comparator Interrupt routine is executed if the ACIE bit is set (one) and the I-bit in SREG is set (one). ACI is cleared by

hardware when executing the corresponding interrupt handling vector. Alternatively, ACI is cleared by writing a logic one to the flag.

#### Bit 3 - ACIE: Analog Comparator Interrupt Enable:

When the ACIE bit is set (one) and the I-bit in the Status Register is set (one), the analog comparator interrupt is activated. When cleared (zero), the interrupt is disabled. For details on the comparator, refer to Page 4-22.

#### Bit 2 - ACIC: Analog Comparator Input Capture enable:

When set (one), this bit enables the Input Capture function in Timer/Counter1 to be triggered by the analog comparator. The comparator output is in this case directly connected to the Input Capture front-end logic, making the comparator utilize the noise canceler and edge select features of the Timer/Counter1 Input Capture interrupt. When cleared (zero), no connection between the analog comparator and the Input Capture function is given. To make the comparator trigger the Timer/Counter1 Input Capture interrupt, the TICIE1 bit in the Timer Interrupt Mask Register (TIMSK) must be set (one).

#### Bits 1,0 - ACIS1, ACIS0: Analog Comparator Interrupt Mode Select:

These bits determine which comparator events that trigger the Analog Comparator interrupt. The different settings are shown in Table 7.

Table 7: ACIS1/ACIS0 Settings

| ACIS1 | ACIS0 | Interrupt Mode                              |

|-------|-------|---------------------------------------------|

| 0     | 0     | Comparator Interrupt on Output Toggle       |

| 0     | 1     | Reserved                                    |

| 1     | 0     | Comparator Interrupt on Falling Output Edge |

| 1     | 1     | Comparator Interrupt on Rising Output Edge  |

Note: When changing the ACIS1/ACIS0 bits, The Analog Comparator Interrupt must be disabled by clearing its Interrupt Enable bit in the ACSR register. Otherwise an interrupt can occur when the bits are changed.

## I/O-Ports

#### Port B

Port B is an 8-bit bi-directional I/O port.

Three data memory address locations are allocated for the Port B, one each for the Data Register - PORTB (\$18), Data Direction Register - DDRB (\$17) and the Port B Input Pins - PINB (\$16). The Port B Input Pins address is read only, while the Data Register and the Data Direction Register are read/write.

All port pins have individually selectable pullups. The Port B output buffers can sink 20mA and thus drive LED displays directly. When pins PB0 to PB7 are used as inputs and are externally pulled low, they will source current (IIL) if the internal pullups are activated.

The Port B pins with alternate functions are shown in the following table:

**Table 8: Port B Pins Alternate Functions**

| Port Pin | Alternate Functions                              |

|----------|--------------------------------------------------|

| PB0      | AIN0 (Analog comparator positive input)          |

| PB1      | AIN1 (Analog comparator negative input)          |

| PB2      | OC0 (Timer/Counter0 Output compare match output) |

| PB5      | MOSI (Data input line for memory downloading)    |

| PB6      | MISO (Data output line for memory uploading)     |

| PB7      | SCK (Master clock input)                         |

When the pins are used for the alternate function the DDRB and PORTB register has to be set according to the alternate function description.

#### THE PORTB DATA REGISTER - PORTB

| Bit           | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0   |                |

|---------------|-------|-----|-----|-----|-----|-----|-----|-----|----------------|

| \$18          | PB7   | PB6 | PB5 | PB4 | PB3 | PB2 | PB1 | PB0 | PORTB          |

| Read/Write    | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W | <del>-</del> . |

| Initial value | 0 - 1 | 0   | 0   | 0   | 0   | 0   | 0   | 0   |                |

#### THE PORT B DATA DIRECTION REGISTER - DDRB

| Bit           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |      |

|---------------|------|------|------|------|------|------|------|------|------|

| \$17          | DDB7 | DDB6 | DDB5 | DDB4 | DDB3 | DDB2 | DDB1 | DDB0 | DDRB |

| Read/Write    | R/W  |      |

| Initial value | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |      |

#### THE PORT B INPUT PIN ADDRESS - PINB

| Bit           | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |      |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| \$16          | PINB7 | PINB6 | PINB5 | PINB4 | PINB3 | PINB2 | PINB1 | PINB0 | PINB |

| Read/Write    | R     | R     | R     | R     | R     | R     | R     | R     |      |

| Initial value | Hi-Z  |      |

The Port B Input Pins address - PINB - is not a register, and this address enables access to the physical value on each Port B pin. When reading PORTB, the PORTB Data Latch is read, and when reading PINB, the logical values present on the pins are read.

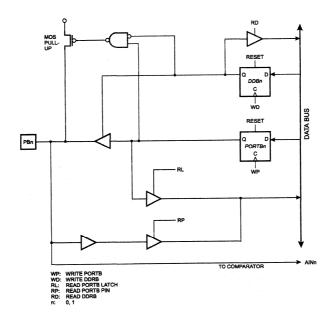

#### **PORTB AS GENERAL DIGITAL I/O**

All 8 bits in port B are equal when used as digital I/O pins.

PBn, General I/O pin: The DDBn bit in the DDRB register selects the direction of this pin, if DDBn is set (one), PBn is configured as an output pin. If DDBn is cleared (zero), PBn is configured as an input pin. If PBn is set (one) and the pin is configured as an input pin, the MOS pull up resistor is activated. To switch the pull up resistor off, the PBn has to be cleared (zero) or the pin has to be configured as an output pin.

Table 9: DDBn Effect on PORTB Pins

| DDBn | PBn | I/O    | Pull up | Comment                                           |

|------|-----|--------|---------|---------------------------------------------------|

| 0    | 0   | Input  | No      | Tri-state (Hi-Z)                                  |

| 0    | 1   | Input  | Yes     | PBn will source current (IIL) if ext. pulled low. |

| 1    | 0   | Output | No      | Push-Pull Zero Output                             |

| 1 1  | . 1 | Output | No      | Push-Pull One Output                              |

n: 7,6...0, pin number.

#### **ALTERNATE FUNCTIONS FOR PORTB**

The alternate pin functions of Port B are:

#### SCK - PORTB, Bit 7:

SCK, Clock input pin for Memory downloading.

#### MISO - PORTB, Bit 6:

MISO, Data output pin for Memory downloading.

#### **MOSI - PORTB, Bit 5:**

MOSI, Data input pin for Memory downloading.

#### OC0 - PORTB, Bit 2:

OC0, Output compare match output: The PB2 pin can serve as an external output when Timer/Counter0 compare matches. The PB2 pin has to be configured as an output (DDB2 is set (one)) to serve this function. See the timer description for further details, and how to enable the output.

#### AIN1 - PORTB, Bit 1:

AIN1, Analog Comparator Positive Input. When configured as an input (DDB1 is cleared (zero)) and with the internal MOS pull up resistor switched off (PB1 is cleared (zero)), this pin also serves as the negative input of the on-chip analog comparator.

#### AIN0 - PORTB, Bit 0:

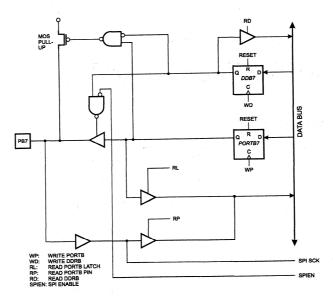

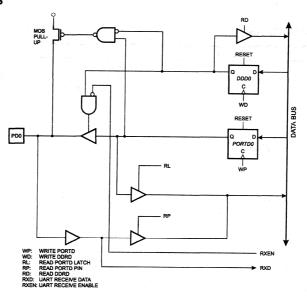

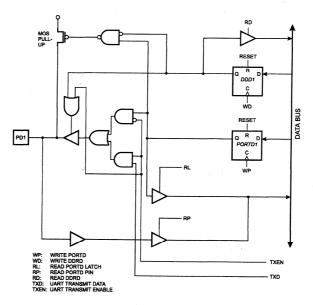

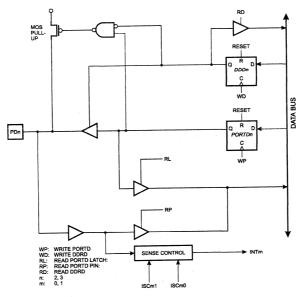

AIN0, Analog Comparator Positive Input. When configured as an input (DDB0 is cleared (zero)) and with the internal MOS pull up resistor switched off (PB0 is cleared (zero)), this pin also serves as the positive input of the on-chip analog comparator.

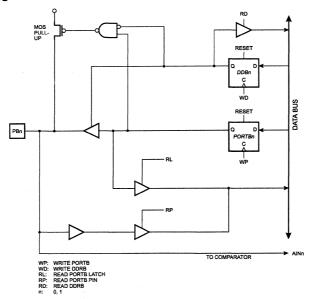

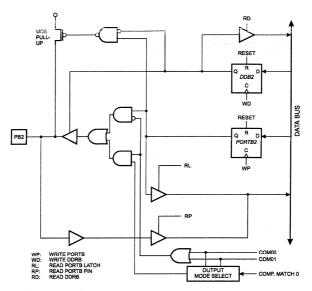

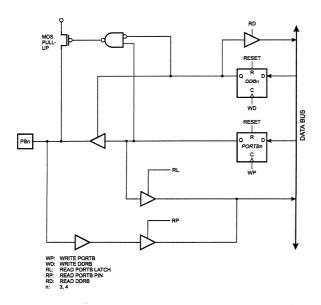

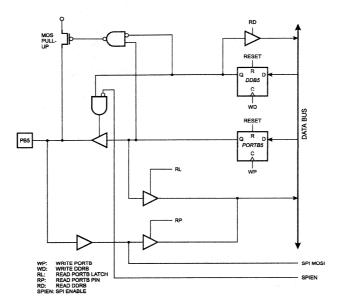

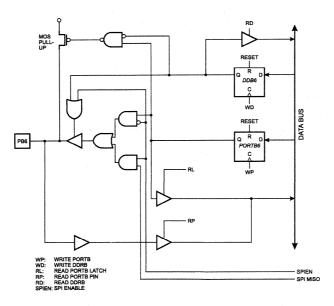

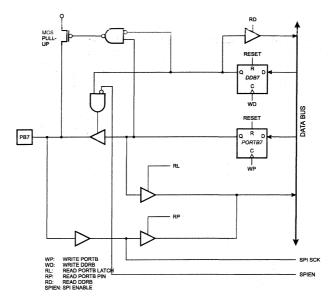

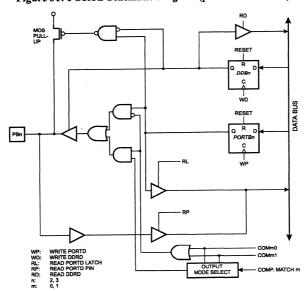

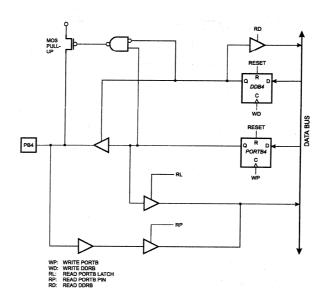

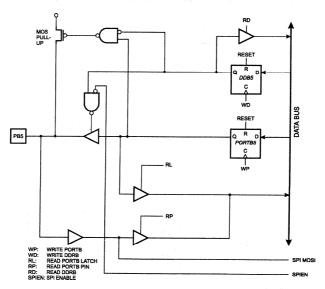

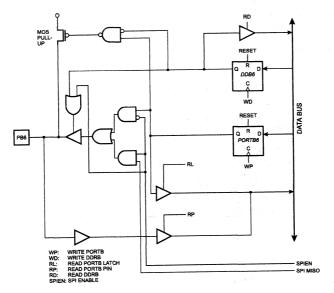

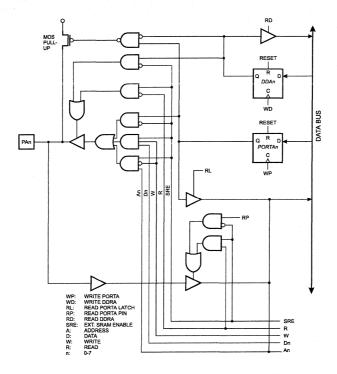

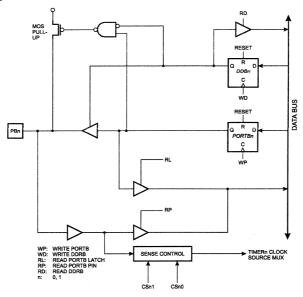

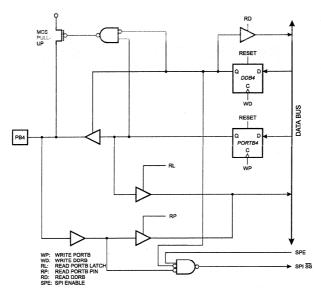

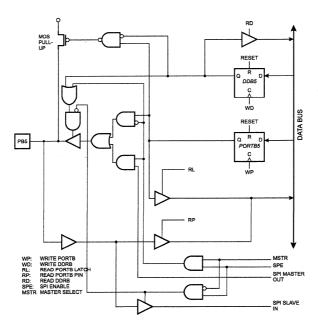

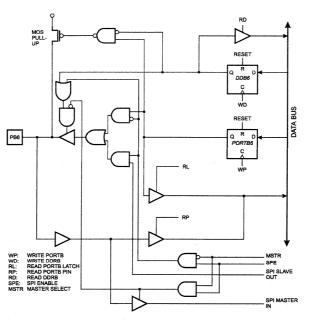

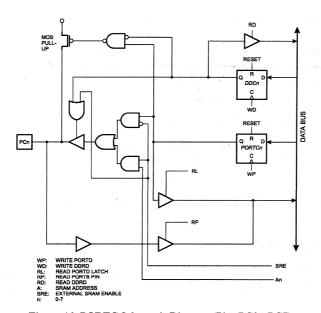

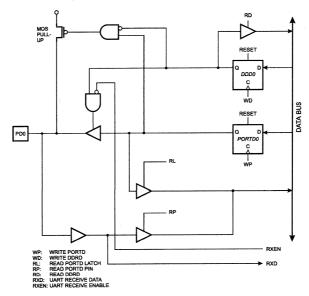

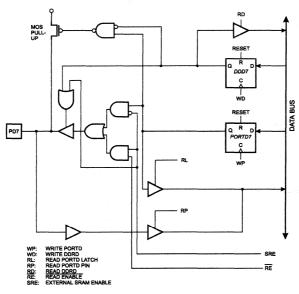

#### PORT B SCHEMATICS

Figure 16: PORTB Schematic Diagram (pins PB0 and PB1)

Figure 17: PORTB Schematic Diagram (Pin PB2)

Figure 18: PORTB Schematic Diagram (Pins PB3 and PB4)

Figure 19: PORTB Schematic Diagram, Pin PB5

Figure 20: PORTB SchematicDiagram, in PB6

Figure 21: PORTB Schematic Diagram, Pin PB7

### Port D

Three data memory address locations are allocated for the Port D, one each for the Data Register - PORTD (\$12), Data Direction Register - DDRD (\$11) and the Port D Input Pins - PIND (\$10). The Port D Input Pins address is read only, while the Data Register and the Data Direction Register are read/write.

Port D has seven bi-directional I/O pins with internal pullups, PD6..PD0. The Port D output buffers can sink 20 mA. As inputs, Port D pins that are externally pulled low will source current (IIL) if the pullups are activated.

Some Port D pins have alternate functions as shown in the following table:

**Table 10: Port D Pins Alternate Functions**

| Port Pin | Alternate Function                  |

|----------|-------------------------------------|

| PD2      | INT0 (External interrupt 0 input)   |

| PD4      | T0 (Timer/Counter 0 external input) |

When the pins are used for the alternate function the DDRD and PORTD register has to be set according to the alternate function description.

#### THE PORTD DATA REGISTER - PORTD

| Bit           | 7 | 6   | 5   | 4   | 3   | 2   | 150 | 0   |        |

|---------------|---|-----|-----|-----|-----|-----|-----|-----|--------|

| \$12          |   | PD6 | PD5 | PD4 | PD3 | PD2 | PD1 | PD0 | PORTD  |

| Read/Write    | R | R/W | -<br>- |

| Initial value | 0 | 0   | 0   | 0   | 0   | 0   | 0   | 0   |        |

#### THE PORT D DATA DIRECTION REGISTER - DDRD

| Bit           | 7 | 6    | 5    | 4    | 3    | 2    | 1    | 0    | _    |

|---------------|---|------|------|------|------|------|------|------|------|

| \$11          | - | DDD6 | DDD5 | DDD4 | DDD3 | DDD2 | DDD1 | DDD0 | DDRD |

| Read/Write    | R | R/W  | -    |

| Initial value | 0 | 0    | 0    | 0    | 0    | 0    | 0    | 0    |      |

#### THE PORT D INPUT PINS ADDRESS - PIND

| Bit           | 7 | 6     | 5     | 4     | 3     | 2     | 1     | 0     | _    |

|---------------|---|-------|-------|-------|-------|-------|-------|-------|------|

| \$10          |   | PIND6 | PIND5 | PIND4 | PIND3 | PIND2 | PIND1 | PIND0 | PIND |

| Read/Write    | R | R     | R     | R     | R     | R     | R     | R     | _    |

| Initial value | 0 | Hi-Z  |      |

The Port D Input Pins address - PIND - is not a register, and this address enables access to the physical value on each Port D pin. When reading PORTD, the PORTD Data Latch is read, and when reading PIND, the logical values present on the pins are read.

#### PORTD AS GENERAL DIGITAL I/O

PDn, General I/O pin: The DDDn bit in the DDRD register selects the direction of this pin. If DDDn is set (one), PDn is configured as an output pin. If DDDn is cleared (zero), PDn is configured as an input pin. If PDn is set (one) when DDDn is configured as an input pin, the MOS pull up resistor is activated. To switch the pull up resistor off, the PDn bit has to be cleared (zero) or the pin has to be configured as an output pin.

Table 11: DDDn Bits Effect on Port D Pins

| DDDn | PDn | I/O    | Pull up | Comment                                           |

|------|-----|--------|---------|---------------------------------------------------|

| 0    | 0   | Input  | No      | Tri-state (Hi-Z)                                  |

| 0    | 1   | Input  | Yes     | PDn will source current (IIL) if ext. pulled low. |

| 1    | 0   | Output | No      | Push-Pull Zero Output                             |

| 1    | 1   | Output | No      | Push-Pull One Output                              |

n: 6...0, pin number.

#### **ALTERNATE FUNCTIONS FOR PORTD**

The alternate functions of Port D are:

#### T0 - PORTD, Bit 4:

T0, Timer/Counter0 clock source: The PD4 pin has to be configured as an input (DDD4 is cleared (zero)) to serve this function. See the Timer description for further details. The internal pull up MOS resistor can be activated as described above.

#### INTO - PORTD, Bit 2:

INT0, External Interrupt source 0: The PD2 pin can serve as an external active low interrupt source to the MCU. The PD2 pin has to be configured as an input (DDD0 is cleared (zero)) to serve this function. The internal pull up MOS resistor can be activated as described above. See the interrupt description for further details, and how to enable the source.

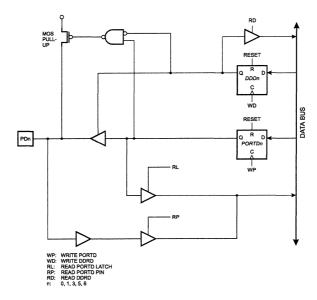

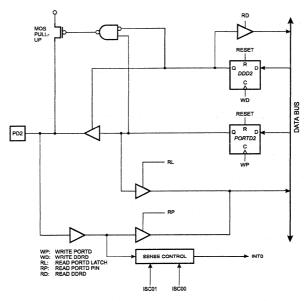

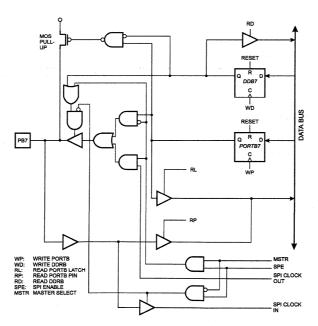

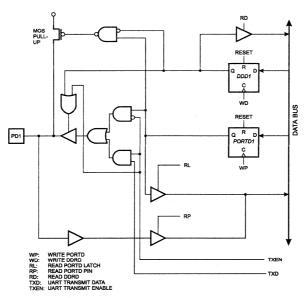

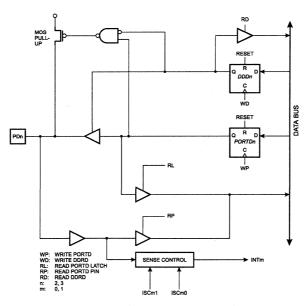

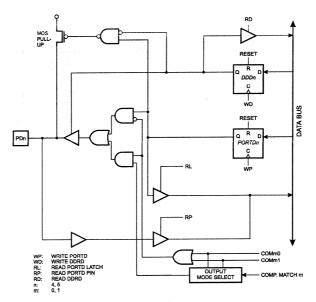

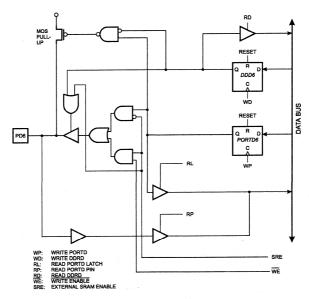

#### PORTD SCHEMATICS

Figure 22: PORTD Schematic Diagram (Pins PD0, PD1, PD3, PD5 and PD6)

Figure 23: PORTD Schematic Diagram (Pin PD2)

Figure 24: PORTD Schematic Diagram (Pin PD4)

# **Memory Programming**

## **Program Memory Lock Bits**

The AT90S1300 MCU provides two lock bits which can be left unprogrammed (U) or can be programmed (P) to obtain the additional features listed in Table 12.

**Table 12: Lock Bit Protection Modes**

| Program Lo | ck Bits |     | Protection Type                     |

|------------|---------|-----|-------------------------------------|

| Mode       | LB1     | LB2 |                                     |

| 1          | U       | U   | No program lock features            |

|            |         |     | Further programming of the Flash is |

| 2          | Р       | U   | disabled                            |

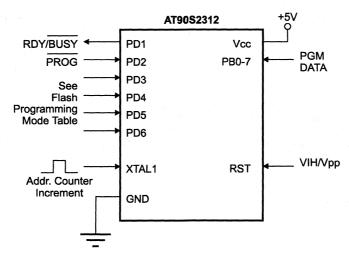

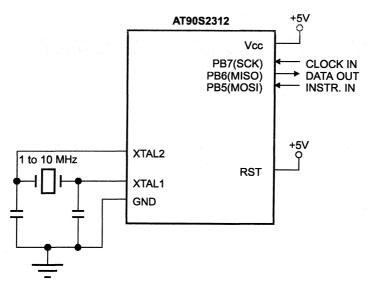

|            |         |     | Same as mode 2, but verify is also  |